譯碼器

譯碼器是電子技術中的一種多輸入多輸出的組合邏輯電路,負責將二進制代碼翻譯為特定的對象(如邏輯電平等),功能與編碼器相反。譯碼器一般分為通用譯碼器和數碼顯示譯碼器兩大類。

數碼電路中,譯碼器(如n線-2n線BCD譯碼器)可以擔任多輸入多輸出邏輯門的角色,能將已編碼的輸入轉換成已編碼的輸出,這裏輸入和輸出的編碼是不同的。輸入使能訊號必須接在譯碼器上使其正常工作,否則輸出將會是一個無效的碼字。譯碼在多路復用、 七劃管和記憶體地址譯碼等應用中是必要的。

二進制解碼器通常實現為獨立集成電路(IC)或更複雜的IC的一部分。在後一種情況下,可以通過諸如VHDL或Verilog等的硬件描述語言來合成解碼器。廣泛使用的解碼器通常以標準化IC的形式提供。

原理[編輯]

譯碼器可以由與門或與非門來負責輸出。若使用與門,當所有的輸入均為高電平時,輸出才為高電平,這樣的輸出稱為「高電平有效」的輸出;若使用與非門,則當所有的輸入均為高電平時,輸出才為低電平,這樣的輸出稱為「低電平有效」的輸出。

更複雜的譯碼器是n線-2n線類型的二進制譯碼器。這類譯碼器是一種組合邏輯電路,能從已編碼的n個輸入,將二進制資訊轉換為2n個獨特的輸出中最大個數的輸出。我們說2n個輸出的最大個數,是因為當n位已編碼資訊中有未使用的位組合時,譯碼器可能會有少於2n個輸出。

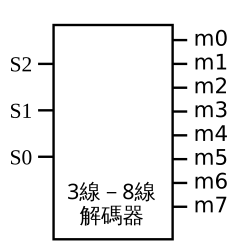

譯碼器包括2線-4線譯碼器、3線-8線譯碼器或4線-16線譯碼器。在有使能訊號輸入的情況下,2個2線-4線譯碼器可以組成1個3線-8線譯碼器,同樣,2個3線-8線譯碼器可以組成1個4線-16線譯碼器。在這類電路設計中,2個3線-8線譯碼器的使能輸入都來自於第四個輸入端,這一輸入在2個3線-8線譯碼器間起到了選擇器的作用t。這使得第四個輸入端可以使2個譯碼器中的任何一個工作,其中第一個譯碼器產生輸出D(0)至D(7),第二個譯碼器產生輸出D(8)至D(15)。包含使能輸入的譯碼器又稱譯碼器-多路分配器。因此,將第四個輸入端作為2個譯碼器共用的輸出就能組成1個4線-16線譯碼器,能產生16個輸出。[1]

二進制解碼器通常實現為獨立集成電路(IC)或更複雜的IC的一部分。在後一種情況下,可以通過諸如VHDL或Verilog之類的硬件描述語言來合成解碼器。廣泛使用的解碼器通常以標準化IC的形式提供。

二進制到一元解碼器[編輯]

二進制到一進制解碼器將每個二進制值轉換為其關聯的一進製表示形式。與n選1(單發)解碼器不同,可以為每個輸入值聲明多個輸出位。這些解碼器可用於每個位均等加權的DAC,以及需要二進制掩碼或窗口的電路。

功能表[編輯]

- 輸入:s0,s1,s2

- 輸出:最小項m0,m1,…,m7

行選擇[編輯]

大多數隨機存取記憶體使用n線-2n線譯碼器來將地址匯流排上已選擇的地址轉換為行地址選擇線中的一個。[2]

指令譯碼器[編輯]

在CPU設計中,指令譯碼器是CPU的一部分,能將儲存在指令暫存器或微程式指令中的位元轉換為能控制CPU其他部分的控制訊號。

8個暫存器組成的簡單CPU會使用指令譯碼器中的3線-8線邏輯譯碼器來選擇暫存器檔案的源暫存器並輸出到ALU以及目的暫存器中,以接受ALU的輸出。典型的CPU指令譯碼器也包括其他很多組件。[3]

參見[編輯]

參考資料[編輯]

- ^ Binary to unary decoder for a video digital to analog converter. [2021-03-24]. (原始內容存檔於2021-04-09). 已忽略未知參數

|gdate=(幫助) - ^ Abdelhadi, Ameer M. S. Architecture of block-RAM-based massively parallel memory structures : multi-ported memories and content-addressable memories. University of British Columbia. 2016 [2021-04-28]. (原始內容存檔於2021-04-30).

- ^ AmeerAbdelhadi/Indirectly-Indexed-2D-Binary-Content-Addressable-Memory-BCAM. GitHub. [2020-02-29]. (原始內容存檔於2020-12-10) (英語).

外部連結[編輯]

| |||||||||||||||||