JTAG

此條目翻譯品質不佳。 |

JTAG是联合测试工作组(Joint Test Action Group)的简称,是在名为标准测试访问端口和边界扫描结构的IEEE的标准1149.1的常用名称。此标准用于驗證設計與測試生產出的印刷電路板功能。

1990年JTAG正式由IEEE的1149.1-1990号文档标准化,在1994年,加入了补充文档对边界扫描描述语言(BSDL)进行了说明。从那时开始,这个标准被全球的电子企业广泛采用。边界扫描几乎成为了JTAG的同义词。

在設計印刷電路板時,目前最主要用在測試積體電路的副區塊,而且也提供一個在嵌入式系統很有用的偵錯機制,提供一個在系統中方便的"後門"。當使用一些偵錯工具像電路內模擬器用JTAG當做訊號傳輸的機制,使得程式設計師可以經由JTAG去讀取整合在CPU上的偵錯模組。偵錯模組可以讓程式設計師偵錯嵌入式系統中的軟體。

電氣特性

JTAG的介面是一種特殊的4/5個接腳介面連到晶片上 ,所以在電路版上的很多晶片可以將他們的JTAG接腳通过Daisy Chain的方式連在一起,并且Probe只需连接到一个“JTAG端口”就可以访问一块印刷電路板上的所有IC。这些连接引脚是:

- TDI(测试数据输入)

- TDO(测试数据输出)

- TCK(测试时钟)

- TMS(测试模式选择)

- TRST(测试复位)可选。

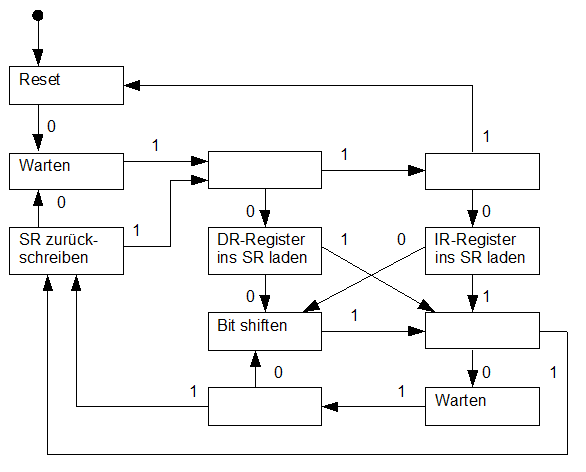

因为只有一条数据线,通信协议有必要像其他串行设备接口,如SPI一样为串列傳輸。时钟由TCK引脚输入。配置是通过TMS引脚采用状态机的形式一次操作一位来实现的。每一位数据在每个TCK时钟脉冲下分别由TDI和TDO引脚传入或传出。可以通过加载不同的命令模式来读取芯片的标识,对输入引脚采样,驱动(或悬空)输出引脚,操控芯片功能,或者旁路(将TDI与TDO连通以在逻辑上短接多个芯片的链路)。TCK的工作频率依芯片的不同而不同,但其通常工作在10-100MHz(每位10-100ns)。

当在集成电路中进行边界扫描时,被处理的信号是在同一块IC的不同功能模块间的,而不是不同IC之间的。

TRST引脚是一个可选的相对待测逻辑低电平有效的复位开关——通常是异步的,但有时也是同步的,依芯片而定。如果该引脚没有定义,则待测逻辑可由同步时钟输入复位指令而复位。

尽管如此,极少消费类产品提供外部的JTAG端口接口,但作为开发样品的残留,这些接口在印刷电路板上十分常见。在研发后,这些接口常常为反向工程提供了非常良好的途径。

常用的扩展

关于制造商的扩展:英飞凌,MIPS EJTAG,飞思卡尔COP, ARM ETM (Extended Trace Macrocell), OnCE etc.

广泛的应用

客户端软件

可以通过使用一些支持JTAG的应用程序来访问JTAG接口。

免费软件

- Very cheap interface working with the CICLaMaB program

- OpenCores JTAG module是一个IP核,它可为你的设计提供JTAG。它是OpenCores工程的一部分。

- UrJTAG (页面存档备份,存于互联网档案馆),born out of the openwince (页面存档备份,存于互联网档案馆) project's JTAG Tools (页面存档备份,存于互联网档案馆),supports a large set of inexpensive IEEE 1284 parallel printer port and USB JTAG cables

- JTAG-ARM9 (页面存档备份,存于互联网档案馆) provides a JTAG access program for the ARM9 processor.

- JTAG for the LART aimed at the LART processor

- JTAG base layer is an attempt at creating a JTAG library

- The uCLinux for Blackfin project have a JTAG-backend for the GNU Debugger and a version specifically for Blackfin based on the openwince work

- JTAG toolkit (页面存档备份,存于互联网档案馆) is a free software JTAG tool suite, including API library and several examples

- OpenOCD is an GPL Open Source GDB Server that currently supports ARM7 and some ARM9 Targets

私有软件

- JTAG ScanWorks (页面存档备份,存于互联网档案馆) JTAG development systems.

- JTAG DFT Analysis (页面存档备份,存于互联网档案馆) JTAG Design for Test software.

- JTAG Technologies (页面存档备份,存于互联网档案馆) Test and programming development systems.

- TopJTAG Probe (页面存档备份,存于互联网档案馆) Interactive JTAG/boundary-scan software for circuit debugging and visualization.

- Green Hills Software (页面存档备份,存于互联网档案馆) MULTI Debugger and Green Hills Probe, Software and hardware supports JTAG and BDM based development on ARM, XScale, PowerPC, MIPS, ColdFire, Blackfin, ARC, TI C6000, v800, StarCore, SH, M32R, and LSI ZSP.

- Ronetix (页面存档备份,存于互联网档案馆) PEEDI, JTAG Emulator and Flash Programmer for ARM7/9, XScale

- SEGGER Microcontroller Systeme GmbH j-link, USB to JTAG interface for ARM cores(J-Flash, J-Mem, RDI Pro Bundle)

- SEGGER Microcontroller Systems LLC (页面存档备份,存于互联网档案馆) j-trace, a USB to Trace Mictor and JTAG interface for ARM cores

- Lauterbach Datentechnik GmbH produce JTAG-based in-circuit emulators the most popular being TRACE 32

- Macraigor Systems LLC (页面存档备份,存于互联网档案馆) JTAG Commander and OCD Commander

- Abatron AG's BDI-2000 acts as a GDB server on your LAN, giving you source-level debugging via JTAG.

- JTAG Emulator Embedded Toolsmiths (页面存档备份,存于互联网档案馆) Guardian-SE JTAG Emulator connects a GDB server on your LAN to the JTAG interface on PowerPC, MIPS, XScale and Arm Processors. This allows: JTAG FLASH Programming, JTAG Emulation and JTAG source-level debugging via JTAG for PowerPC, MIPS, XScale and ARM Processors.

- XJTAG (页面存档备份,存于互联网档案馆) Development System

- Göpel electronic (页面存档备份,存于互联网档案馆) SCANFLEX

- Corelis (页面存档备份,存于互联网档案馆) ScanExpress

- yaJFP (页面存档备份,存于互联网档案馆) Zheyuan Technlogies

外部链接

- 什么是JTAG那么,我怎么样才能利用它呢? (页面存档备份,存于互联网档案馆)

- JTAG Tutorial (页面存档备份,存于互联网档案馆)关于JTAG或边界扫描的简介。

- JTAG/Boundary-scan explained知识库以及工业连接。

- JTAG FAQ (页面存档备份,存于互联网档案馆)

- OpenJTAG Wiki

- JTAG边界扫描接口的一个简明介绍

- JTAG Scan Educator - Ver. 2 (Rev. A) - 一个DOS下的教学软件,JTAG Scan Educator,介绍了IEEE 1149.1边界扫描标准的基本情况,包括框架协议,以及所需的指令集。

- K9JTAG - 一个便宜的为ARM微控制器的JTAG调试器而自制的并行端口。

- Boundary-Scan Testing/JTAG (页面存档备份,存于互联网档案馆) - www.SiliconFarEast.com

- Segger J-Link (页面存档备份,存于互联网档案馆)(JTAG仿真器)

- Segger-US J-Link(JTAG仿真器)

- Circuit Cellar Article (SOFTWARE BREAKPOINTS IN FLASH MEMORY FOR ARM MCUs)