MSI協議

在計算機科學中,MSI協議是一個在多處理器系統中運行的基本的緩存一致性協議。與其他緩存一致性協議一樣,協議名稱中「M,S,I」三個字母表明高速緩存行可能的狀態。

概述

[編輯]在MSI中,緩存中包含的每個塊可能處於以下三種狀態之一:

- Modified(已修改):塊已在緩存中已被修改,緩存中的數據與後備存儲器(例如內存)中的數據不一致。具有「M」狀態的塊的緩存在該塊被替換時需要將其中的內容寫回後備存儲。

- Shared(共享):塊未被修改,並在至少一個處理器的緩存中以只讀狀態存在。高速緩存可以將其替換而不將其中的數據寫回後備存儲。

- Invalid(無效):該塊不存在於當前緩存中,或者因為總線請求而被標記為無效。如果要將某個塊存儲在該緩存中,則必須首先從內存或另一個高速緩存中獲取該塊。[1]

這些一致性狀態通過高速緩存和後備存儲之間的通信進行維護。 當緩存中的某個塊被讀或寫時,或者當緩存通過總線接收到其他緩存發出的讀寫信號時,它需要據此來做出動作並調整自己的狀態。

當緩存收到讀取請求時,如果一個塊處於「M」或「S」狀態,則它會直接提供數據。但如果塊尚未被裝入緩存(處於「I」狀態),則在裝入該塊之前,必須先要保證該地址的數據不會在其他緩存的緩存塊中處於「M」狀態。不同的緩存架構處理這個問題的方式是不同的。例如,總線架構通常使用總線監聽來解決此問題,此時讀取請求將廣播給所有的緩存。其他架構,例如緩存目錄,則通過一個中介(例如目錄)來獲取哪一個緩存擁有緩存塊的最新副本。如果另一個緩存中有處於「M」狀態的塊,則它必須將數據寫回後備存儲,並回到「S」或「I」狀態。在數據寫回之後,緩存可以通過後備存儲或者其他緩存中處於「S」狀態的對應塊獲取內容。之後緩存會答覆讀取請求。在提供的數據後,緩存塊處於「S」狀態。

當緩存收到寫請求時,如果這個塊處於"M"狀態,則緩存只需要修改本地的數據。 如果塊處於"S"狀態,則緩存必須通知其他的具有處於「S」狀態的同樣的塊的高速緩存將其換出(置為「I」狀態)。和上文所述類似,這種通知可以通過總線監聽或緩存目錄來進行。完成後緩存會修改本地的數據。 如果塊處於"I"狀態,則緩存必須通知其他的具有處於「S」或「M」狀態的同樣的塊的高速緩存將其換出(置為「I」狀態)。如果塊在另一個緩存中處於"M"狀態,那麼它必須先將數據寫回後備存儲或者將其提供給請求數據的緩存。如果此時緩存尚未裝載該塊的數據,則修改前要先將其從後備存儲讀入。在數據被修改之後,緩存塊處於"M"的狀態。

對於任何給定的兩個緩存,如果他們具有對應相同地址的緩存行,則允許的狀態如下表所示:

| M | S | I | |

|---|---|---|---|

| M | |||

| S | |||

| I |

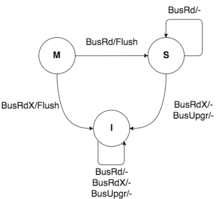

狀態機

[編輯]

處理器向高速緩存發出的請求包括:

- PrRd:處理器請求讀取一個緩存塊。

- PrWr:處理器請求改寫一個緩存塊。

此外,還有總線方面的請求。 包括:

- BusRd:當某個處理器的高速緩存的讀操作出現未命中,它會向總線發送一個BusRd請求,並預期能夠收到該緩存塊的數據。

- BusRdX:當某個處理器的高速緩存的寫操作出現未命中,它會向總線發送一個BusRdX請求,預期能夠收到該緩存塊的數據,並且使其他處理器中對應相同地址的緩存塊無效。

- BusUpgr:當某個處理器的高速緩存的寫操作命中時,它它會向總線發送一個BusUpgr,使其他處理器中對應相同地址的緩存塊無效。

- Flush:該請求表明一個緩存塊正在被寫回內存。

狀態轉移:

- 處於Invalid(無效)狀態的緩存塊:

- 在PrRd,BusRd發出時,狀態變為Shared(共享)。

- 在PrWr,BusRdX發出時,狀態變為Modified(已修改)。

- 在BusRd,BusRdX或BusUpg發出時,狀態保持Invalid(無效)。

- 處於Shared(共享)狀態的緩存塊:

- 在PrRd,BusRd發出時,狀態保持Shared(共享)。

- 在PrWr,BusUpgr發出時,狀態變為Modified(已修改)。

- 在BusRdX或BusUpgr發出時,狀態變為Invalid(無效)。

- 處於Modified(已修改)狀態的緩存塊

- 在PrRd或PrWr發出時,狀態保持Modified(已修改)。

- 在BusRd發出時,緩存塊被寫回,狀態變為Shared(共享)。

- 在BusRdX發出時,緩存塊被寫回,狀態變為Invalid(無效)。[2]

使用

[編輯]變種

[編輯]現代化的系統使用的MSI協議的變種以減少保持緩存一致性所需要的通信量。MESI協議增加了一個Exclusive(獨占)狀態,以減少對於只存在於一個高速緩存的塊的寫操作造成的通信。MOSI協議增加了一個Owned(持有)狀態,以減少對於被其他緩存讀取過的高速緩存的塊的寫回操作造成的通信。MOESI協議同時做了這兩件事情。

相關條目

[編輯]參考文獻

[編輯]- ^ Fuchsen, R. How to address certification for multi-core based IMA platforms: Current status and potential solutions. Digital Avionics Systems Conference (DASC), 2010 IEEE/AIAA 29th. 2010-10-01: 5.E.3–1–5.E.3–11 [2017-05-17]. doi:10.1109/DASC.2010.5655461. (原始內容存檔於2019-10-18).

- ^ Solihin, Yan. Fundamentals of Parallel Multicore Architecture. Chapman & Hall/CRC Computational Science Series. 2016.

- ^ Suh, Taeweon. INTEGRATION AND EVALUATION OF CACHE COHERENCE PROTOCOLS FOR MULTIPROCESSOR SOCS (PDF). December 2006. (原始內容存檔 (PDF)於2017-05-10).