ΔΣ调制

Delta-Sigma(ΔΣ)调制(或称Sigma-Delta(ΣΔ)调制、SDM,中文译作积分-微分调制)是一种数字模拟互相转换的实做方法,它是把高比特清晰度低频率信号用脉冲密度调制编码为低比特清晰度高频率信号的一种方法(PCM转PWM),可以将量化失真移往更高频率、减少滤除时对目标频率的影响,推导自delta调制原理的模拟至数字或是数字至模拟转换技术。ADC或是DAC可借由低成本的CMOS制程实现此一技术,也就是像数字IC一样的制程。基于上述理由,即便本技术早在1960年代已经提出,但是要到近年来由于半导体技术精进才得以普遍的使用。几乎所有的模拟IC制造商都有提供Sigma-Delta转换器产品。

原理

[编辑]

ADC可被认为是一个压控震荡器,控制电压为被测量的电压,线性和比例性由负回授决定。振荡器输出为一个脉冲串,每个脉冲为已知,常量,幅度=V且持续时间为dt,因此有一个已知的积分=Vdt但是变化的分离间隔。脉冲的间隔由回授电路决定,所以一个低输入电压产出一个脉冲间的长间隔;而一个高输入电压产生一个短间隔。实际上,忽略开关错误,脉冲间的间隔与该间隔内输入电压的平均成反比,因此在该间隔ts内,是一个平均输入电压的样本,与v/ts成正比。

最终的输出数是输入电压(该电压由脉冲计数决定)的数字化在一个固定加总间隔=Ndt产出一个计数,Σ。脉冲串的积分为ΣVdt其在时间间隔Ndt内被生成,因此输入电压在加总周期内的平均为VΣ/N,而且是平均的平均所以只遭受很小的变化。

达成的精度取决于已知V的精度和一个计数内N的精度及分辨率。

上面描述的脉冲可被认为是迪拉克方程的形式化分析,计数可被认为Σ。在ADC的转化中,正是这些脉冲串被delta-sigma调制所传递。 ΔΣ架构主要是在对信号的大小做一个粗略的估计,然后量测其误差,将其积分并补偿之,最后输出的平均值会等于输入信号的平均值(若误差的积分为有限值)。

积分器的数量决定了ΔΣ调制电路的阶数(Order),图2中所示为二阶ΔΣ电路;阶数越高时,noise shaping效果越好,但相对付出代价是稳定度必须妥善考量。

ΔΣ调制电路也可以用量化器的输出比特数来分类,当使用N阶的比较器时,输出为log2N-bit;基于线性度的考量,常见的ΔΣ电路为1-bit组态,也就是输出仅有两个位准:0或1。

Noise Shaping效果

[编辑]由微分器、积分器构成的ΔΣ调制电路,会因其微分特性而对量化噪声(Quantization noise)产生一种高通滤波的效果。一般线性PCM中产生的量化噪声平均分布在各频率上,基于前述特性,可以将量化噪声推往高频,而产生noise shaping功效。将取样频率设高,因人耳可听到的频段相对低频,而此时将已经被推往高频的量化噪声以低通滤波器滤除,便可以得到量化噪声较少的原信号。

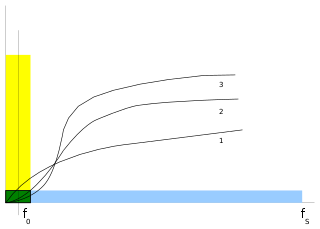

当ΔΣ调制阶数越多时,noise shaping效果也会越显著,如图所示为1~3阶ΔΣ的noise shaping效果。

AD转换

[编辑]对于AD转换,可以把它想象为一个压控振荡器。被测量电压是压控振荡器控制电压,线性度和比例由负回授回路决定。振荡器的输出是一连串的已知脉冲,宽度dt,幅度V,积分为Vdt。但是,各个脉冲之间的时间间隔是可变的。脉冲间隔由回授电路决定,低电压产生长间隔,高电压产生短间隔。事实上,如果不考虑转换误差,脉冲间隔和此段时间输入电压的平均值成反比。最终,在固定的时间周期Ndt内,输出计数值Σ将反映出输入电压的大小。脉冲的积分为ΣVdt。平均电压为VΣ/N。精确度取决于V的准确度,N中单位计数的准确度和清晰度。可以通过改变采样总时间Ndt,或者固定比例倒计时等方法,改变输入电压和对应数字电压比例。可以将脉冲视为δ(delta)函数,计数值为Σ(sigma)。

目的

[编辑]Delta-sigma调制将模拟电压信号转换为脉冲频率或脉冲密度,可理解为脉冲密度调制(Pdm)。只要脉冲的定时和符号可以恢复,则以已知固定速率表示比特的正脉冲和负脉冲串行在接收器处非常容易产生、发送和准确地再生。给定来自增量-西格玛调制器的这样的脉冲串行,可以以足够的精度重建原始波形。相反,在不转换为脉冲流而只是直接传输模拟信号的情况下,系统中的所有噪声都将被添加到模拟信号中,从而降低其质量。使用Pdm作为信号表示是脉冲编码调制(PCM)的替代,以奈奎斯特率(Nyquist Rate)采样和量化为多比特码。

过采样(Oversampling)

[编辑]

ΔΣ调制是一种过采样技术,可降低感兴趣频段(图5中的绿色)中的噪声,从而避免使用高精度模拟电路作为抗混叠滤波器。Nyquist转换器(黄色)和过采样转换器(蓝色)中的总量化噪声是相同的,但它分布在不同的频谱上。在ΔΣ转换器中,噪声在低频率时会进一步降低,这是感兴趣的信号所在的频段,而在较高频率时,噪声会增加,在那里它可以被过滤掉。这种技术称为噪声整形。

对于一阶Delta-Sigma调制器,噪声由传递函数为Hn(Z)=[1−z−1]的滤波器整形。假设采样频率fs与感兴趣的信号频率f0相比较大,则期望信号带宽中的量化噪声可以近似为:

- .

类似地,对于二阶Delta-Sigma调制器,噪声由传递函数为Hn(Z)=[1−z−1]2的滤波器整形。带内量化噪声可以近似为:

- .

一般而言,对于N阶ΔΣ调制器,带内量化噪声的方差为:

- .

当采样频率加倍时,对于一个N阶ΔΣ调制器,信噪比提高了6N+3分贝。过采样率越高,信噪比越高,分辨率以位为单位越高。

过采样给出的另一个关键方面是速度/分辨率的权衡。放在调制器后面的抽取滤波器不仅在感兴趣的频带内对整个采样信号进行滤波(在较高频率处去除噪声),而且还降低了信号的频率,提高了信号的分辨率。这是通过对较高数据速率的比特流进行某种平均来获得的。

参见

[编辑]参考资料

[编辑]- "Sigma-delta techniques extend DAC resolution"[永久失效链接] article by Tim Wescott 2004-06-23

- "Tutorial on Designing Delta-Sigma Modulators: Part I"[失效链接](2004-03-30)and "Part II"[失效链接](2004-04-01)a tutorial by Mingliang Liu

- "Gabor Temes' Publications" (页面存档备份,存于互联网档案馆)

- "Bruce Wooley's Delta-Sigma Converter Projects" (页面存档备份,存于互联网档案馆)

- "An Introduction to Delta Sigma Converters" (页面存档备份,存于互联网档案馆)(which covers both ADC's and DAC's sigma-delta)

- "Demystifying Sigma-Delta ADCs" (页面存档备份,存于互联网档案馆)。This in-depth article covers the theory behind a Delta-Sigma analog-to-digital converter.

- "Motorola digital signal processors: Principles of sigma-delta modulation for analog-to-digital converters"

- "One-Bit Delta Sigma D/A Conversion Part I: Theory" article by Randy Yates presented at the 2004 comp.dsp conference

相关出版品

[编辑]- J. Candy, G. Temes, Oversampling Delta-sigma Data Converters, ISBN 0-87942-285-8

- S. Norsworthy, R. Schreier, G. Temes, Delta-Sigma Data Converters, ISBN 0-7803-1045-4

- Mingliang Liu, Demystifying Switched-Capacitor Circuits, ISBN 0-7506-7907-7

- R. Schreier, G. Temes, Understanding Delta-Sigma Data Converters, ISBN 0-471-46585-2