ΔΣ調變

Delta-Sigma(ΔΣ)調變(或稱Sigma-Delta(ΣΔ)調變、SDM,中文譯作積分-微分調變)是一種數位類比互相轉換的實做方法,它是把高位元解析度低頻率信號用脈衝密度調製編碼為低位元解析度高頻率信號的一種方法(PCM轉PWM),可以將量化失真移往更高頻率、減少濾除時對目標頻率的影響,推導自delta調變原理的類比至數位或是數位至類比轉換技術。ADC或是DAC可藉由低成本的CMOS製程實現此一技術,也就是像數位IC一樣的製程。基於上述理由,即便本技術早在1960年代已經提出,但是要到近年來由於半導體技術精進才得以普遍的使用。幾乎所有的類比IC製造商都有提供Sigma-Delta轉換器產品。

原理

[編輯]

ADC可被認為是一個壓控震盪器,控制電壓為被測量的電壓,線性和比例性由負迴授決定。振盪器輸出為一個脈衝串,每個脈衝為已知,常量,幅度=V且持續時間為dt,因此有一個已知的積分=Vdt但是變化的分離間隔。脈衝的間隔由迴授電路決定,所以一個低輸入電壓產出一個脈衝間的長間隔;而一個高輸入電壓產生一個短間隔。實際上,忽略開關錯誤,脈衝間的間隔與該間隔內輸入電壓的平均成反比,因此在該間隔ts內,是一個平均輸入電壓的樣本,與v/ts成正比。

最終的輸出數是輸入電壓(該電壓由脈衝計數決定)的數字化在一個固定加總間隔=Ndt產出一個計數,Σ。脈衝串的積分為ΣVdt其在時間間隔Ndt內被生成,因此輸入電壓在加總周期內的平均為VΣ/N,而且是平均的平均所以只遭受很小的變化。

達成的精度取決於已知V的精度和一個計數內N的精度及分辨率。

上面描述的脈衝可被認為是迪拉克方程的形式化分析,計數可被認為Σ。在ADC的轉化中,正是這些脈衝串被delta-sigma調製所傳遞。 ΔΣ架構主要是在對訊號的大小做一個粗略的估計,然後量測其誤差,將其積分並補償之,最後輸出的平均值會等於輸入訊號的平均值(若誤差的積分為有限值)。

積分器的數量決定了ΔΣ調變電路的階數(Order),圖2中所示為二階ΔΣ電路;階數越高時,noise shaping效果越好,但相對付出代價是穩定度必須妥善考量。

ΔΣ調變電路也可以用量化器的輸出位元數來分類,當使用N階的比較器時,輸出為log2N-bit;基於線性度的考量,常見的ΔΣ電路為1-bit組態,也就是輸出僅有兩個位準:0或1。

Noise Shaping效果

[編輯]由微分器、積分器構成的ΔΣ調變電路,會因其微分特性而對量化雜訊(Quantization noise)產生一種高通濾波的效果。一般線性PCM中產生的量化雜訊平均分布在各頻率上,基於前述特性,可以將量化雜訊推往高頻,而產生noise shaping功效。將取樣頻率設高,因人耳可聽到的頻段相對低頻,而此時將已經被推往高頻的量化雜訊以低通濾波器濾除,便可以得到量化雜訊較少的原訊號。

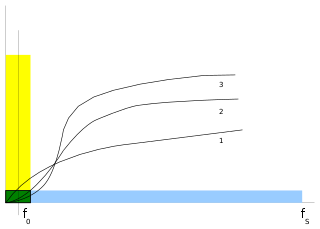

當ΔΣ調變階數越多時,noise shaping效果也會越顯著,如圖所示為1~3階ΔΣ的noise shaping效果。

AD轉換

[編輯]對於AD轉換,可以把它想象為一個壓控振盪器。被測量電壓是壓控振盪器控制電壓,線性度和比例由負回授迴路決定。振盪器的輸出是一連串的已知脈衝,寬度dt,幅度V,積分為Vdt。但是,各個脈衝之間的時間間隔是可變的。脈衝間隔由回授電路決定,低電壓產生長間隔,高電壓產生短間隔。事實上,如果不考慮轉換誤差,脈衝間隔和此段時間輸入電壓的平均值成反比。最終,在固定的時間周期Ndt內,輸出計數值Σ將反映出輸入電壓的大小。脈衝的積分為ΣVdt。平均電壓為VΣ/N。精確度取決於V的準確度,N中單位計數的準確度和解析度。可以通過改變採樣總時間Ndt,或者固定比例倒計時等方法,改變輸入電壓和對應數字電壓比例。可以將脈衝視為δ(delta)函數,計數值為Σ(sigma)。

目的

[編輯]Delta-sigma調製將模擬電壓信號轉換為脈衝頻率或脈衝密度,可理解為脈衝密度調製(Pdm)。只要脈衝的定時和符號可以恢復,則以已知固定速率表示比特的正脈衝和負脈衝序列在接收器處非常容易產生、發送和準確地再生。給定來自增量-西格瑪調製器的這樣的脈衝序列,可以以足夠的精度重建原始波形。相反,在不轉換為脈衝流而只是直接傳輸模擬信號的情況下,系統中的所有雜訊都將被添加到模擬信號中,從而降低其質量。使用Pdm作為信號表示是脈衝編碼調製(PCM)的替代,以奈奎斯特率(Nyquist Rate)採樣和量化為多比特碼。

過採樣(Oversampling)

[編輯]

ΔΣ調製是一種過採樣技術,可降低感興趣頻段(圖5中的綠色)中的噪聲,從而避免使用高精度模擬電路作為抗混疊濾波器。Nyquist轉換器(黃色)和過採樣轉換器(藍色)中的總量化噪聲是相同的,但它分布在不同的頻譜上。在ΔΣ轉換器中,噪聲在低頻率時會進一步降低,這是感興趣的信號所在的頻段,而在較高頻率時,噪聲會增加,在那裡它可以被過濾掉。這種技術稱為噪聲整形。

對於一階Delta-Sigma調製器,噪聲由傳遞函數為Hn(Z)=[1−z−1]的濾波器整形。假設採樣頻率fs與感興趣的信號頻率f0相比較大,則期望信號帶寬中的量化噪聲可以近似為:

- .

類似地,對於二階Delta-Sigma調製器,噪聲由傳遞函數為Hn(Z)=[1−z−1]2的濾波器整形。帶內量化噪聲可以近似為:

- .

一般而言,對於N階ΔΣ調製器,帶內量化噪聲的方差為:

- .

當採樣頻率加倍時,對於一個N階ΔΣ調製器,信噪比提高了6N+3分貝。過採樣率越高,信噪比越高,分辨率以位為單位越高。

過採樣給出的另一個關鍵方面是速度/分辨率的權衡。放在調製器後面的抽取濾波器不僅在感興趣的頻帶內對整個採樣信號進行濾波(在較高頻率處去除噪聲),而且還降低了信號的頻率,提高了信號的分辨率。這是通過對較高數據速率的比特流進行某種平均來獲得的。

參見

[編輯]參考資料

[編輯]- "Sigma-delta techniques extend DAC resolution"[永久失效連結] article by Tim Wescott 2004-06-23

- "Tutorial on Designing Delta-Sigma Modulators: Part I"[失效連結](2004-03-30)and "Part II"[失效連結](2004-04-01)a tutorial by Mingliang Liu

- "Gabor Temes' Publications" (頁面存檔備份,存於網際網路檔案館)

- "Bruce Wooley's Delta-Sigma Converter Projects" (頁面存檔備份,存於網際網路檔案館)

- "An Introduction to Delta Sigma Converters" (頁面存檔備份,存於網際網路檔案館)(which covers both ADC's and DAC's sigma-delta)

- "Demystifying Sigma-Delta ADCs" (頁面存檔備份,存於網際網路檔案館)。This in-depth article covers the theory behind a Delta-Sigma analog-to-digital converter.

- "Motorola digital signal processors: Principles of sigma-delta modulation for analog-to-digital converters"

- "One-Bit Delta Sigma D/A Conversion Part I: Theory" article by Randy Yates presented at the 2004 comp.dsp conference

相關出版品

[編輯]- J. Candy, G. Temes, Oversampling Delta-sigma Data Converters, ISBN 0-87942-285-8

- S. Norsworthy, R. Schreier, G. Temes, Delta-Sigma Data Converters, ISBN 0-7803-1045-4

- Mingliang Liu, Demystifying Switched-Capacitor Circuits, ISBN 0-7506-7907-7

- R. Schreier, G. Temes, Understanding Delta-Sigma Data Converters, ISBN 0-471-46585-2