可程式化邏輯陣列

外观

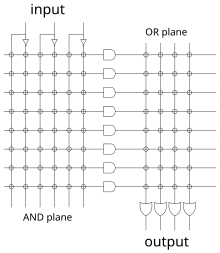

可程式化邏輯陣列(英語:Programmable Logic Array,縮寫:PLA)是一種可以實作組合邏輯電路的可程式邏輯裝置。PLA有一組可編程的AND閘,其連接到一組可編程的OR閘,如此可以達到:「只在合乎設定條件時才允許產生邏輯訊號輸出。」PLA有2^N個AND閘來輸入N個變數,並且需要M個OR閘來輸出M個結果。PLA如此的邏輯閘佈局能用來規劃大量的邏輯函式,這些邏輯函式必須先以積項(有時是多個積項)的原始形式進行齊一化。

PLA與可程式陣列邏輯裝置(PAL)的差別為PLA的AND閘、OR閘皆可修改。

歷史

[编辑]1970年,德州儀器根據IBM的唯讀關聯記憶體(ROAM)開發了一個有可編程光罩的IC(TMS2000)。此IC藉由改變金屬層來達成可編程的功能。TMS2000有17個輸入、18個輸出以及8個JK正反器作為記憶體。 同時,德州儀器將此裝置命名為PLA。[1]

步驟

[编辑]- 將所需邏輯化成積項之和(Sum of Products)(SOP)

- 將SOP化簡至最簡型式

- 決定輸入的AND陣列產生需要的積項(Product term)

- 決定OR陣列的輸入產生需要的和項(Sum term)

- 決定反向陣列的連接

- 開始編程PLA

應用

[编辑]在PLA的應用中,有一種是用來控制資料路徑,在指令集內事先定義好邏輯狀態,並用此來產生下一個邏輯狀態(透過條件分支)。

舉例來說,如果目前機器(指整個邏輯系統)處於二號狀態,如果接下來的執行指令中含有一個立即值(偵測到立即值的欄位)時,機器就從第二狀態轉成四號狀態,並且也可以進一步定義進入第四狀態後的接續動作。因此PLA等於扮演(晶片)系統內含的邏輯狀態圖(state diagram)角色。

除了PLA外,其他常用的可程式邏輯裝置還有可程式化陣列邏輯(PAL)、複雜可程式邏輯裝置(CPLD)以及現場可程式邏輯閘陣列(FPGA)。

參見

[编辑]- 可程式化邏輯裝置(PLD)

- 現場可程式化邏輯門陣列(FPGA)

- 可程式化陣列邏輯(PAL)

- 通用陣列邏輯(GAL)

參考文獻

[编辑]- ^ Andres, Kent. A Texas Instruments Application Report: MOS programmable logic arrays.. Texas Instruments. October 1970. Bulletin CA-158.

外部連結

[编辑]- Programmable Logic Array (PLA). cmsc311. University of Maryland. 2003 [2016-03-06]. (原始内容存档于2017-12-14).

- PLA (programmable logic array). Java Applet. University of Hamburg. [2016-03-06]. (原始内容存档于2013-01-15).