可程式化逻辑阵列

外观

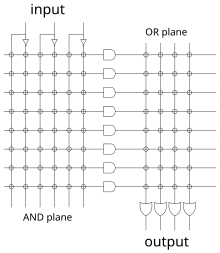

可程式化逻辑阵列(英语:Programmable Logic Array,缩写:PLA)是一种可以实作组合逻辑电路的可程式逻辑装置。PLA有一组可编程的AND闸,其连接到一组可编程的OR闸,如此可以达到:“只在合乎设定条件时才允许产生逻辑讯号输出。”PLA有2^N个AND闸来输入N个变数,并且需要M个OR闸来输出M个结果。PLA如此的逻辑闸布局能用来规划大量的逻辑函式,这些逻辑函式必须先以积项(有时是多个积项)的原始形式进行齐一化。

PLA与可程式阵列逻辑装置(PAL)的差别为PLA的AND闸、OR闸皆可修改。

历史[编辑]

1970年,德州仪器根据IBM的唯读关联记忆体(ROAM)开发了一个有可编程光罩的IC(TMS2000)。此IC借由改变金属层来达成可编程的功能。TMS2000有17个输入、18个输出以及8个JK正反器作为记忆体。 同时,德州仪器将此装置命名为PLA。[1]

步骤[编辑]

- 将所需逻辑化成积项之和(Sum of Products)(SOP)

- 将SOP化简至最简型式

- 决定输入的AND阵列产生需要的积项(Product term)

- 决定OR阵列的输入产生需要的和项(Sum term)

- 决定反向阵列的连接

- 开始编程PLA

应用[编辑]

在PLA的应用中,有一种是用来控制资料路径,在指令集内事先定义好逻辑状态,并用此来产生下一个逻辑状态(透过条件分支)。

举例来说,如果目前机器(指整个逻辑系统)处于二号状态,如果接下来的执行指令中含有一个立即值(侦测到立即值的栏位)时,机器就从第二状态转成四号状态,并且也可以进一步定义进入第四状态后的接续动作。因此PLA等于扮演(晶片)系统内含的逻辑状态图(state diagram)角色。

除了PLA外,其他常用的可程式逻辑装置还有可程式化阵列逻辑(PAL)、复杂可程式逻辑装置(CPLD)以及现场可程式逻辑闸阵列(FPGA)。

参见[编辑]

- 可程式化逻辑装置(PLD)

- 现场可程式化逻辑门阵列(FPGA)

- 可程式化阵列逻辑(PAL)

- 通用阵列逻辑(GAL)

参考文献[编辑]

- ^ Andres, Kent. A Texas Instruments Application Report: MOS programmable logic arrays.. Texas Instruments. October 1970. Bulletin CA-158.

外部链接[编辑]

- Programmable Logic Array (PLA). cmsc311. University of Maryland. 2003 [2016-03-06]. (原始内容存档于2017-12-14).

- PLA (programmable logic array). Java Applet. University of Hamburg. [2016-03-06]. (原始内容存档于2013-01-15).

| |||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||||||

|