计数器

在逻辑代数与电脑运算中,计数器是存储(有时还有显示)特定事件或过程发生次数的装置,往往与定时器信号有关联。最常见的类型是有“时钟”输入线和多输出线的时序逻辑电路。输出线的值代表在二进制或BCD计数系统的数。每个施加到时钟输入的脉冲都会使计数器增加或是减少。

计数器电路通常由多个触发器级联连接而成。计数器在数字电路中使用非常广泛,会制成集成电路晶片以及作为更大集成电路的一部分。

电子计数器

[编辑]在电子学中,可以用像触发器等寄存器型电路来实现计数器,也存在各种类型:

- 异步(纹波)计数器 – 改变状态位用作后续状态触发器的的时钟

- 同步计数器 – 所有状态位都在单一时钟的控制下

- 十进制计数器 – 每级经过10个状态

- 递增/递减计数器 – 借由输入信号的控制,可以让计数器递增或是递减

- 环形计数器 – 由移位寄存器组成,但有额外连接成环状的反馈电路

- 约翰逊记数器 – 扭环形计数器

- 级联计数器

- 模数计数器。

每种计数器都有不同的用途。计数器在其本质上是数字系统,用二进制计数。不过许多类型的计数器电路可作为数字电路的基本模块,例如4000系列晶片中实现的不同计数器。

有时使用计数序列而不使用自然二进制序列会比较方便—如BCD计数器、线性反馈移位寄存器及格雷码计数器。

计数器用于数字时钟和计时器中,出现在烤箱定时器以及VCR时钟等内部。[1]

异步(纹波)计数器

[编辑]

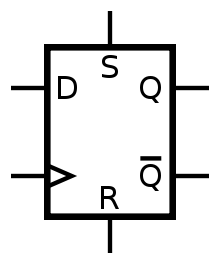

最简单的异步(纹波)计数器是一个将反向输出反馈给D输入的D型触发器。该电路可以存储一个比特,因此在它溢出(从0重新开始)之前可以从零计数到一。该计数器每个时钟周期会递增一次,两个时钟周期会溢出,故每个周期会从0转换到1,再从1转换到0。异步计数器会产生一个新的新时钟,频率是输入时钟频率的一半,占空比50%。

如果这个输出再接到D型触发器(其反向输出也反馈给D输入)作为时钟,将会得到计数速度为其一半的另一个1位计数器。把它们集成在一起,就产生了两位计数器:

| 周期 | Q1 | Q0 | (Q1:Q0)dec |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 2 | 1 | 0 | 2 |

| 3 | 1 | 1 | 3 |

| 4 | 0 | 0 | 0 |

可以继续添加触发器(反向输出需作为触发器自己的输入),并使用前一个触发器的输出作为时钟信号。结果称作纹波计数器,可以计数到2n - 1其中n为计数器的位数(触发器的级数)。纹波计数器会受到级与级之间溢出“纹波”的不稳定输出的影响,但纹波计数器常常应用在时脉信号除频的应用上。一位的异步计数器可以输入一个时钟信号,输入一个频率为一半的时钟信号。二位的异步计数器可以输入一个频率为四分之一的时钟信号……越多位的计数器其除频比率就更高,在此应用下,瞬时的计数值不是主要考量,而整体除频的比率才是重点。

因为用触发器的输出作为时钟,因此计数的资料比特之间会有时钟偏移,也因此异步计数器的技术无法和标准的同步电路设计兼容。

同步计数器

[编辑]

在同步计数器中,所有触发器的时钟输入端连接在一起,由输入脉冲触发。因此,所有的触发器的状态同时改变(并行)。下面的电路是一个4位同步计数器。FF0的J和K输入接高电平。FF0的输出接FF1的J和K输入,FF0与FF1输出经过AND闸后连接到FF2的J和K输入,FF0、FF1与FF2输出输出经过AND闸后连接到FF3的J和K输入(右图中是FF2的J输入和FF2的输出,两者在逻辑上是等价的)。接与门的输出接收的反馈。若各触发器以递增方式编号,简单实现此线路的方式就是让每一个触发器在编号较小的触发器全部为高电位时反相(这也是右图中所描述的情形)。例如比特1在比特0为高电位时反相,比特2在比特0和1均为高电位时反相,比特3在比特0,1,2均为高电位时反相……。

一般以硬件为基础的计数器是以此架构进行。同步计数器也可以用硬件的有限状态机实现,其架构比较复杂,但可以进行更平滑,更稳定的转态。

十进制计数器

[编辑]

十进制计数器是用十进制计数的计数器,可能是用二进码十进数(BCD)计数,就像7490 IC所作的一样,或是用其他的编码方式(如加三码)。

十进制计数器的每个位数需要数0到9,然后复归到0,一般的二进制四位数计数器可以数十进制的一位数字,若是用二进码十进数的计数方式,只要像右图一样加入NAND闸,其输入为FF2及FF4,输出为每个闸的CLR输入即可。在每一个脉波信号时,计数器会加1,当加到二进制1010(十进制的10时),将所有的闸都清除为零,此信号经过处理后也是进位信号,表示已经算到十了。

环形计数器

[编辑]

环形计数器是循环的移位寄存器[2],其中的触发器中只有一个是高电位输出,其余的都是低电位输出。移位寄存器是由触发器层叠而成,若将最后一个触发器的输出接到第一个触发器的输入,形成一个环,即为环形计数器。

一般来说,环形计数器中循环的资料是只有一个比特为1的资料,因此任一时刻只有一个触发器输出为高电位。例如四比特的环形计数器,其初始状态为1000,之后会是0001,0010,0100,1000……等。n比特的环形计数器会循环n次,每计数一次的汉明距离是2。

约翰逊记数器

[编辑]

约翰逊记数器(Johnson counter)也称为尾端切换环形计数器(switchtail ring counter)、扭环计数器(twisted-ring counter)、走动环状记数器(walking-ring counter)或莫比斯计数器(Moebius counter)是修改过的环形计数器,最后一个触发器的输出反相后再接到第一个触发器[3][4][5]。n比特的环形计数器会循环2n次,例如例如四比特的环形计数器,其初始状态为0000,之后会是1000, 1100, 1110, 1111, 0111, 0011, 0001, 0000, ……等。每计数一次的汉明距离是1。

约翰逊记数器可以用D型触发器或是JK触发器组合,可以用在像数字模拟转换器之类的应用。

电脑科学中的计数器

[编辑]在可计算性理论中,计数器被视为是一种存储器,可以存储一个自然数,一般从0开始,可以到任意长度。计数器一般会和有限状态机(FSM)一起考虑,可以进行以下的步骤:

- 判断计数器是否为零

- 计数器加一

- 计数器减一,若已经为零,计数器不变化。

以下的状态机是以其功能来排序,前面的功能比后面的强:

- 有二个计数器的确定型或非确定型有限状态机

- 加上一个堆栈的非确定有限状态自动机

- 加上一个计数器的非确定有限状态自动机

- 加上一个计数器的确定有限状态自动机

- 没有计数器或堆栈的确定型或非确定型有限状态机

针对第一个或是最后一个,有限状态机可以是确定型,也可以是非确定型。前二者及最后一个是依乔姆斯基谱系排列。

上述的第一种有限状态机,也就是有二个计数器的有限状态机,其计算能力和图灵机等效。

网页计数器

[编辑]网页计数器是一个计算机程序,可以显示特定网页浏览的次数。在设置后,只要有网页浏览器链接到此网页,网页计数器就会加一。

网页计数器一般会用数码图像或是纯文字显示,也可能以早期的机械计数器方式显示。图案可以用不同的字体显示,也可以用不同的风格,像是类似里程表的显示方式。

网页计数器在1980年代及1990年代相当流行,后来已被更多细节及更复杂的网站流量量测所取代。

以电脑为基础的计数器

[编辑]许多自动化系统用电脑或是手提电脑来监控机器的各种参数,并且产生资料。计数器可以计数资料,例如制作的工作数、生产批号、计算使用材料的数量等。

机械计数器

[编辑]

在发明电子装置之前,就已经用机械式的计数器,像手揿号码计数器即为一例。机械式计数器一般是由几个接在同一个轴上的转盘组成,转盘上有一到九的数字,每有一个事件,最右侧转盘都会加一。最左侧以外的其他转盘侧面都有突起处,在旋转一圈,。会让左侧的转盘进行一格。像脚踏车或是汽车上用的里程表就有这类计数器,像磁带录音机及加油机中也有。Veeder-Root公司是机械计数器的大厂商之一,因此公司的名称有时也用做此计数器的名称[6]。

在资料处理产业的早期,机械计数器也用在制表机中来计算总和。

参见

[编辑]参考文献

[编辑]- ^ Synchronous counter, Digital, Play hookey, [2015-05-06], (原始内容存档于2010-01-07).

- ^ 邓元庆、关宇、贾鹏、石会. 数字设计基础与应用. 北京: 清华大学出版社. : 133. ISBN 978-7-302-21406-9 (中文(中国大陆)).

- ^ Singh, Arun Kumar. Digital Principles Foundation of Circuit Design and Application. New Age Publishers. 2006 [2015-05-06]. ISBN 81-224-1759-0. (原始内容存档于2014-07-24).

- ^ Horowitz, Paul; Hill, Winfield. The Art of Electronics. Cambridge University Press. 1989 [2015-05-06]. ISBN 0-521-37095-7. (原始内容存档于2014-07-24).

- ^ Graf, Rudolf F. Modern Dictionary of Electronics. Newnes. 1999 [2015-05-06]. ISBN 0-7506-9866-7. (原始内容存档于2014-07-24).

- ^ VR History, Veeder, [2015-05-06], (原始内容存档于2012-09-12).