同相器

| 基本逻辑闸 | |

| 缓冲 | 非 |

| 与 | 与非 |

| 或 | 或非 |

| 异或 | 同或 |

| 蕴含 | 蕴含非 |

| 输入 A |

输出 BUF(A) |

| 0 | 0 |

| 1 | 1 |

缓冲闸[1](英语:Buffer gate)又称缓冲门、同闸、是闸(英语:YES gate)[2]、驱动器或放大器,是一种会输出一个与输入相同逻辑讯号的逻辑闸,是数位逻辑中实现缓冲或放大用的逻辑闸,也可使当成数位逻辑中实现逻辑命题的逻辑闸,功能见右侧真值表。

虽然直接复制输入为输出似乎是一件毫无意义的事情,它也有实际的应用,例如一个微弱的信号源可以透过缓冲闸而增强讯号[3]。缓冲闸前后的逻辑电平是不变的,因此有时也作为数位中继器[4]。

缓冲闸与直接导通不同,缓冲闸与其他逻辑闸一样都有延迟,因此缓冲闸有时被做为数位电路的讯号延迟元件[5]。

缓冲闸是一种单一输入逻辑闸,另外一种单一输入逻辑闸是反相器,功能正好相反。

概述

[编辑]下列包括逻辑闸的3种符号:形状特征型符号(ANSI/IEEE Std 91-1984)、IEC矩形国标符号(IEC 60617-12)和不再使用的DIN符号(DIN 40700)。其他的逻辑闸符号详见逻辑门符号表。

| 表达式 | 符号 | 功能表 | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| ANSI/IEEE Std 91-1984 | IEC 60617-12 | DIN 40700 | ||||||||

|

|

|

| |||||||

性质

[编辑]因为缓冲闸的输出端讯号等于输入端讯号,所以它并不会执行任何逻辑运算功能。但在数位电路中有时会需要使用缓冲闸来增加讯号强度,例如有一个逻辑闸的扇出数为4[注 1],但是该逻辑电路需要将其输出再接到超过五个逻辑闸,此时可以在中间串接一个缓冲闸,由于缓冲闸不会使电路的逻辑行为发生改变,因此此举可以确保电路的逻辑行为正确无误。另外在单纯NMOS或PMOS的逻辑电路中也可以使用缓冲闸来减少PMOS对高电平的电压降与NMOS对低电平的电压升。

此外由于逻辑闸运作时都会有延迟,但缓冲闸不会执行任何逻辑运算功能,因此也可以做为电路中讯号延迟的元件。

电路实现

[编辑]

-

NMOS缓冲闸

-

PMOS缓冲闸

-

TTL缓冲闸

-

静态CMOS缓冲闸

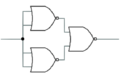

缓冲闸电路输出电压所代表的逻辑电平与输入相同,这刚好与反相器相反,由于逻辑对合律,因此缓冲闸可由两个反相器组合而成,反相器可以仅用一个NMOS电晶体或一个PMOS连接一个电阻来构建,因此缓冲闸也可以使用串接的两个NMOS电晶体或PMOS电晶体构成,而CMOS则是将这两种加以组合,达到互补的效果。

积体电路

[编辑]六同相器是一种包含6个缓冲闸的积体电路。例如,7407 TTL晶片有14个引脚,4050 CMOS晶片有16个引脚,两种晶片都各有2个引脚用于电源供电/基准电压,12个引脚用于6个缓冲闸的输入和输出(4050有2个引脚悬空)[6]。此外,741G34也是一种缓冲闸[7],但里面只有单一个缓冲闸。

备选方案

[编辑]-

利用反相器实现的缓冲闸

-

利用及闸实现的缓冲闸

-

利用或闸实现的缓冲闸

-

利用反及闸实现的缓冲闸

-

利用反或闸实现的缓冲闸

缓冲闸只要是逻辑输出等于逻辑输入的组合皆能使用,但不能使用电线代替,有些情况可以先用电压跟随器代替,但可能会有潜在的问题,最安全的方式是将两个反相器串接。

由于缓冲闸要实现的等同于逻辑命题,因此只要输入与输出相等的函数皆能使用,例如逻辑的:幂等律、有界律、对合律与吸收律。

| 幂等律 | ||

| 有界律 | ||

| 对合律 | ||

| 吸收律 |

最简单的两种方式是将或闸或与闸的两个输入接在一起即可完成一个缓冲闸[8]。另外,也能使用被认为是“通用的逻辑闸电路”的反及闸与反或闸[9]来实现。若用反及闸实现缓冲闸,则将两个反及闸的两个输入接在一起,然后将之串接;若用反或闸实现缓冲闸,则将两个反或闸的四个输入接在一起作为输入,然后将两个输出接在第三个反或闸的两个输入即完成一个缓冲闸。

三态逻辑运用

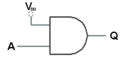

[编辑]

一般逻辑闸输出的高电位大部分是使用VDD端接高电位或电源而完成,但若将缓冲闸的VDD端接也作为输入的话则可以达成三态逻辑的效果[10]。 这个效果则允许输出端在0和1两种逻辑电平之外呈现高阻态,等效于将输出的影响从后级电路中移除。这允许多个电路共同使用同一个输出线(例如汇流排)。

| 输入 A B |

输出 C | |

| 0 | 1 | 0 |

| 1 | 1 | |

| X | 0 | Z |

单一输入逻辑闸

[编辑]缓冲闸是一种单一输入逻辑闸,另外一种单一输入逻辑闸是反相器。在布林代数中,单一输入的布林函数共有四种:

其中两种就是缓冲闸与反相器,分别实现逻辑命题与逻辑非,而另外两种分别为逻辑永真以及逻辑永假。

| 逻辑闸 | 逻辑命题 | 逻辑非 | 逻辑永真 | 逻辑永假 |

| 缓冲闸 | 相反闸 | 恒真闸 | 恒假闸 | |

| 输入 A |

输出 BUF(A) |

输出 |

输出 永真 |

输出 永假 |

| 0 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

-

恒真闸的IEC记号

-

恒假闸的IEC记号

-

蕴含闸组成的恒真闸

但在数位逻辑电路中通常不会出现恒真闸与恒假闸,因为恒真闸实际上就是指短路、电源或高电位(逻辑真)的供应元件,反之恒假闸就是指断路或接地,且这两种门的输出与输入无关。

参见

[编辑]注释

[编辑]- ^ 输出端可接的标准负载个数的最大值

参考文献

[编辑]- ^ buffer gate (页面存档备份,存于互联网档案馆) terms.naer.edu.tw 国家教育研究院 2003-6 [2015-10-1]

- ^ YES gates (页面存档备份,存于互联网档案馆) 2012.igem.org [2015-10-1]

- ^ Buffer gate (页面存档备份,存于互联网档案馆) logic.ly [2015-10-1]

- ^ The “Buffer” Gate (页面存档备份,存于互联网档案馆) allaboutcircuits.com [2015-10-1]

- ^ Logic gates (页面存档备份,存于互联网档案馆) 章节1:Inverter (NOT Gate) and Buffer, 第二部分:Buffer Gate, macao.communications.museum [2015-10-1]

- ^ Texas Instruments:4050b CMOS六同相缓冲器/转换器 (页面存档备份,存于互联网档案馆),资料表:CMOS Hex Buffer/Converters (页面存档备份,存于互联网档案馆)

- ^ 741G34(SN74LVC1G34)的资料表 (页面存档备份,存于互联网档案馆) ti.com [2015-10-1]

- ^ logic gate (页面存档备份,存于互联网档案馆) 段落 YES gate, cpuville.com [2015-10-1]

- ^ Mano, M. Morris and Charles R. Kime. Logic and Computer Design Fundamentals, Third Edition. Prentice Hall, 2004. p. 73.

- ^ Tri-state use buffer gate (页面存档备份,存于互联网档案馆) lectronics-tutorials.ws [2015-10-1]