印刷電路板

此條目需要補充更多來源。 (2016年11月14日) |

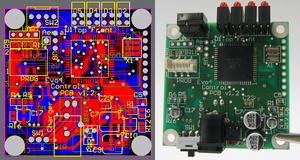

印刷電路板,又稱印製電路板,印刷線路板,常用英文縮寫PCB(Printed circuit board)或PWB(Printed wire board),是電子元件的支撐體,在這其中有金屬導體作為連接電子元器件的線路。

傳統的電路板,採用印刷蝕刻阻劑的工法,做出電路的線路及圖面,因此被稱為印刷電路板或印刷線路板。由於電子產品不斷微小化跟精細化,目前大多數的電路板都是採用貼附蝕刻阻劑(壓膜或塗佈),經過曝光顯影後,再以蝕刻做出電路板。

pcb[1] (頁面存檔備份,存於網際網路檔案館)最早使用的是紙基覆銅印製板。自半導體晶體管於20世紀50年代出現以來,對印製板的需求量急劇上升。特別是集成電路的迅速發展及廣泛應用,使電子設備的體積越來越小,電路布線密度和難度越來越大,這就要求印製板要不斷更新。目前印製板的品種已從單面板發展到雙面板、多層板和撓性板;結構和質量也已發展到超高密度、微型化和高可靠性程度;新的設計方法、設計用品和制板材料、制板工藝不斷湧現。

歷史

[編輯]

在印製電路板出現之前,電子元件之間的互連都是依靠電線直接連接而組成完整的線路。現在,電路麵包板只是作為有效的實驗工具而存在,而印刷電路板在電子工業中已經成了占據絕對統治的地位。

20世紀初,人們為了簡化電子機器的製作,減少電子零件間的配線,降低製作成本等優點,於是開始鑽研以印刷的方式取代配線的方法。三十年間,不斷有工程師提出在絕緣的基板上加以金屬導體作配線。而最成功的是1925年,美國的 Charles Ducas 在絕緣的基板上印刷出線路圖案,再以電鍍的方式在絕緣基材上印刷出導體線路圖案,稱為加成法。[1][2]

直至1936年,奧地利人保羅·愛斯勒(Paul Eisler)在英國發表箔膜技術[1],他在一個收音機裝置內採用了印刷電路板;而在日本,宮本喜之助以噴附配線法[3]成功申請專利。[4]而兩者中 Charles Ducas、宮本喜之助的做法是只加上所需的配線;而Paul Eisler的方法與現今的印刷電路板最為相似,即在覆蓋金屬箔的絕緣基板上選擇性塗覆抗蝕劑,刻蝕掉非必要銅區製備電子線路,這類做法稱為減去法。[2]雖然如此,但因為當時的電子零件發熱量大,兩者的基板也難以配合使用,以致未有正式的實用作,不過也使印刷電路技術更進一步。[1]

1941年,美國在滑石上漆上銅膏作配線,以製作近接信管。1943年,美國人將該技術大量使用於軍用收音機內。1947年,環氧樹脂開始用作製造基板。同時美國國家標準局開始研究以印刷電路技術形成線圈、電容器、電阻器等製造技術。1948年,美國正式認可這個發明用於商業用途。自20世紀50年代起,發熱量較低的電晶體大量取代真空管的地位,印刷電路版技術才開始被廣泛採用,當時以蝕刻箔膜技術為主流[1]。1950年,日本使用玻璃基板上以銀漆作配線;和以酚醛樹脂製的紙質酚醛基板(CCL)上以銅箔作配線。[1]1951年,聚酰亞胺的出現,使樹脂的耐熱性再進一步,也製造聚亞醯胺基板。[1]1953年,Motorola開發出電鍍貫穿孔法的雙面板。這方法也應用到後期的多層電路板上。[1]印刷電路板廣泛被使用10年後的60年代,其技術也日益成熟。而自從Motorola的雙面板問世,多層印刷電路板(Multi-Layer Board,MLB)開始出現,使配線與基板面積比更為提高。

1960年,V. Dahlgreen以印有電路的金屬箔膜貼在熱可塑性的塑膠中,造出軟性印刷電路板。[1] 1961年,美國的Hazeltine Corporation參考電鍍貫穿孔法,製作出多層板。[1]1967年,發表增層法之一的「Plated-up technology」。[1][5]1969年,FD-R以聚醯亞胺製造軟性印刷電路板。[1]1979年,Pactel發表增層法之一的「Pactel法」。[1]1984年,NTT開發薄膜迴路的「Copper Polyimide法」。[1]1988年,西門子公司開發Microwiring Substrate的增層印刷電路板。[1]

1990年,IBM開發「表面增層線路」(Surface Laminar Circuit,SLC)的增層印刷電路板。[1]1995年,松下電器開發ALIVH的增層印刷電路板。[1] 1996年,東芝開發B2it的增層印刷電路板。[1]就在眾多的增層印刷電路板方案被提出的1990年代末期,增層印刷電路板也正式大量地被實用化。

21世紀初前後, 積層法MLB和撓性印製電路板(Flexible PrintedCircuit,FPC)快速發展,片式元器件小型化以及高密度安裝方式,提高了電子產品互連密度。21世紀20年代,印製電路板向着高輸入/輸出(Input/Ouput,I/O)密度、高精細度(窄線寬/ 線距,Line/Space,L/S)、高集成度不斷演進,呈現一體化集成和三維安裝的特徵。[2]

製造印刷電路板

[編輯]基材

[編輯]基材普遍是以基板的絕緣及強化部分作分類,常見的原料為電木板、玻璃纖維板,以及各式的塑膠板。而PCB的製造商普遍會以一種以玻璃纖維不織物料以及環氧樹脂組成的絕緣預浸漬材料(prepreg),再以和銅箔壓製成銅箔基板備用。

而常見的基材及主要成份有:

- FR-1 ──酚醛棉紙,這基材通稱電木板(比FR-2較高經濟性)

- FR-2 ──酚醛棉紙,

- FR-3 ──棉紙、環氧樹脂

- FR-4 ──玻璃布(Woven glass)、環氧樹脂

- FR-5 ──玻璃布、環氧樹脂

- FR-6 ──毛面玻璃、聚酯

- G-10 ──玻璃布、環氧樹脂

- CEM-1 ──棉紙、環氧樹脂(阻燃)

- CEM-2 ──棉紙、環氧樹脂(非阻燃)

- CEM-3 ──玻璃布、環氧樹脂

- CEM-4 ──玻璃布、環氧樹脂

- CEM-5 ──玻璃布、多元酯

- AlN ──氮化鋁

- SIC ──碳化硅

金屬塗層

[編輯]金屬塗層除了有基板上的配線外,也可以是基板線路跟電子元件焊接的地方。此外,由於不同的金屬價格不同,因此直接影響生產的成本。另外,每種金屬的可焊性、接觸性,電阻阻值等等不同,這也會直接影響元件的效能。

常用的金屬塗層有:

線路設計

[編輯]印製電路板的設計是以電路原理圖為藍本,實現電路使用者所需要的功能。印刷電路板的設計主要指版圖設計,需要內部電子元件、金屬連線、通孔和外部連結的佈局、電磁保護、熱耗散、串音等各種因素。優秀的線路設計可以節約生產成本,達到良好的電路性能和散熱性能。簡單的版圖設計可以用手工實現,但複雜的線路設計一般也需要藉助計算機輔助設計(CAD)實現,而著名的設計軟體有OrCAD、Pads (也即PowerPCB)、Altium designer(也即Protel)、FreePCB、CAM350、AutoCAD以及開源軟件KiCad等。

電路板的基本組成

[編輯]目前的電路板,主要由以下組成

- 線路與圖面(Pattern):線路是做為原件之間導通的工具,在設計上會另外設計大銅面作為接地及電源層。線路與圖面是同時做出的。

- 介電層(Dielectric):用來保持線路及各層之間的絕緣性,俗稱為基材

- 孔(Through hole / via):導通孔可使兩層次以上的線路彼此導通,較大的導通孔則做為零件插件用,另外有非導通孔(nPTH)通常用來作為表面貼裝定位,組裝時固定螺絲用

- 防焊油墨(Solder resistant /Solder Mask) :並非全部的銅面都要吃錫上零件,因此非吃錫的區域,會印一層隔絕銅面吃錫的物質(通常為環氧樹脂),避免非吃錫的線路間短路。根據不同的工藝,分為綠油、紅油、藍油。

- 絲印(Legend /Marking/Silk screen):此為非必要的結構,主要的功能是在電路板上標註各零件的名稱、位置框,方便組裝後維修及辨識用。

- 表面處理(Surface Finish):由於銅面在一般環境中,很容易氧化,導致無法上錫(焊錫性不良),因此會在要吃錫的銅面上進行保護。保護的方式有噴錫(HASL),化金(ENIG),化銀(Immersion Silver),化錫(Immersion Tin),有機保焊劑(OSP),方法各有優缺點,統稱為表面處理。

基本製作

[編輯]根據不同的技術可分為消除和增加兩大類過程。

減去法

[編輯]減去法(Subtractive),是利用化學品或機械將空白的電路板(即鋪有完整一塊的金屬箔的電路板)上不需要的地方除去,餘下的地方便是所需要的電路。

- 絲網印刷:把預先設計好的電路圖製成絲網遮罩,絲網上不需要的電路部分會被蠟或者不透水的物料覆蓋,然後把絲網遮罩放到空白線路板上面,再在絲網上油上不會被腐蝕的保護劑,把線路板放到腐蝕液中,沒有被保護劑遮住的部份便會被蝕走,最後把保護劑清理。

- 感光板:把預先設計好的電路圖制在透光的膠片遮罩上(最簡單的做法就是用打印機印出來的投影片),同理應把需要的部份印成不透明的顏色,再在空白線路板上塗上感光顏料,將預備好的膠片遮罩放在電路板上照射強光數分鐘,除去遮罩後用顯影劑把電路板上的圖案顯示出來,最後如同用絲網印刷的方法一樣把電路腐蝕。

- 刻印:利用銑床或雷射彫刻機直接把空白線路上不需要的部份除去。

加成法

[編輯]加成法(Additive),現在普遍是在一塊預先鍍上薄銅的基板上,覆蓋光阻劑(D/F),經紫外光曝光再顯影,把需要的地方露出,然後利用電鍍把線路板上正式線路銅厚增厚到所需要的規格,再鍍上一層抗蝕刻阻劑-金屬薄錫,最後除去光阻劑(這製程稱為去膜),再把光阻劑下的銅箔層蝕刻掉。

半加成法

[編輯]半加成法是在基材絕緣介質表面,首先沉積一層薄銅,然後在其上覆蓋抗蝕劑,選擇性遮蓋非目標區域,之後再利用電鍍沉積一層厚銅,最後除去抗蝕劑和閃蝕掉薄層基銅完成電子線路構建。[2]

多層製作

[編輯]積層法

[編輯][1] 積層法是製作多層印刷電路板的方法之一。是在製作內層後才包上外層,再把外層以減去法或加成法所處理。不斷重複積層法的動作,可以得到再多層的多層印刷電路板則為順序積層法。

- 內層製作

- 積層編成(即黏合不同的層數的動作)

- 積層完成(減去法的外層含金屬箔膜;加成法)

- 鑽孔

- 減去法

- Panel電鍍法

- 全塊PCB電鍍

- 在表面要保留的地方加上阻絕層(resist,防止被蝕刻)

- 蝕刻

- 去除阻絕層

- Pattern電鍍法

- 在表面不要保留的地方加上阻絕層

- 電鍍所需表面至一定厚度

- 去除阻絕層

- 蝕刻至不需要的金屬箔膜消失

- Panel電鍍法

- 加成法

- 令表面粗糙化

- 完全加成法(full-additive)

- 在不要導體的地方加上阻絕層

- 以無電解銅組成線路

- 部分加成法(semi-additive)

- 以無電解銅覆蓋整塊PCB

- 在不要導體的地方加上阻絕層

- 電解鍍銅

- 去除阻絕層

- 蝕刻至原在阻絕層下無電解銅消失

- 減去法

增層法

[編輯]增層法是製作多層印刷電路板的方法之一,顧名思義是把印刷電路板一層一層的加上。每加上一層就處理至所需的形狀。

ALIVH

[編輯]ALIVH(Any Layer Interstitial Via Hole,Any Layer IVA)是日本松下電器開發的增層技術。這是使用芳香聚醯胺(Aramid)纖維布料為基材[1]。

- 把纖維布料浸在環氧樹脂成為「黏合片」(prepreg)

- 雷射鑽孔

- 鑽孔中填滿導電膏

- 在外層黏上銅箔

- 銅箔上以蝕刻的方法製作線路圖案

- 把完成第二步驟的半成品黏上在銅箔上

- 積層編成

- 再不停重覆第五至七的步驟,直至完成

B2it

[編輯]B2it(Buried Bump Interconnection Technology)是東芝開發的增層技術。

- 先製作一塊雙面板或多層板

- 在銅箔上印刷圓錐銀膏

- 放黏合片在銀膏上,並使銀膏貫穿黏合片

- 把上一步的黏合片黏在第一步的板上

- 以蝕刻的方法把黏合片的銅箔製成線路圖案

- 再不停重覆第二至四的步驟,直至完成

注文

[編輯]"FirstPCB"[失效連結] "Seeed Studio" (頁面存檔備份,存於網際網路檔案館) "Elecrow" (頁面存檔備份,存於網際網路檔案館) "Makerfabs" (頁面存檔備份,存於網際網路檔案館) "PCBONLINE" (頁面存檔備份,存於網際網路檔案館)

產業現狀

[編輯]由於印製電路板的製作處於電子設備製造的後半程,因此被稱為電子工業的下游產業。幾乎所有的電子設備都需要印製電路板的支援,因此印製電路板是全球電子元件產品中市場占有率最高的產品。目前日本、中國大陸、臺灣、西歐和美國為主要的印製電路板製造基地。

PCB設計軟件

[編輯]- Altium Designer —— 一體化的電子產品開發系統。

- OrCAD —— 電子設計自動化套裝軟件,用於電子工程師設計印刷電路板。

- KiCad —— 是用於印刷電路板設計的自由軟件,最初由法國人Jean-Pierre Charras於1992年推出,現由KiCad開發者團隊維護。KiCad目前支持英語、法語、德語、意大利語、中文、日語等23個語言版本。

- 立創EDA —— 由嘉立創印刷電路板板廠推出的網頁在線印刷電路板設計工具,亦有離線版本。

參見

[編輯]參考文獻

[編輯]- ^ 1.00 1.01 1.02 1.03 1.04 1.05 1.06 1.07 1.08 1.09 1.10 1.11 1.12 1.13 1.14 1.15 1.16 1.17 1.18 1.19 增層、多層印刷電路板技術 ISBN 957-21-3192-3

- ^ 2.0 2.1 2.2 2.3 Li, Peng; Yu, Junyi; Luo, Suibin; Lai, Zhiqiang; Xiao, Bin; Yu, Shuhui; Sun, Rong. Cu deposition technologies for build-up film substrates towards FC-BGA. SCIENTIA SINICA Chimica. 2023-10-01, 53 (10). ISSN 1674-7224. doi:10.1360/SSC-2023-0130 (英語).

- ^ メタリコン法吹着配線方法(特許119384号)

- ^ 《4.2 積層体の構造の概要》-[[日本專利局]](特許庁) (PDF). [2008-06-15]. (原始內容 (PDF)存檔於2011-03-23).

- ^ R.L. Beadles: Interconnections and Encapsulation, AD 654-630, vol.14 of "Integrated Silicon Device Technology" ASD-IRD-63-316, Research Triangle Institute, 1967, May

- ^ 6.0 6.1 6.2 魏雄。《PowerPCB 5.0.1 印製電路板設計與實踐》北京:電子工業出版社,2006年10月,3-4。 ISBN 7-121-03298-8