解码器

解码器是电子技术中的一种多输入多输出的组合逻辑电路,负责将二进制代码翻译为特定的对象(如逻辑电平等),功能与编码器相反。解码器一般分为通用解码器和数字显示解码器两大类。

数字电路中,解码器(如n线-2n线BCD解码器)可以担任多输入多输出逻辑门的角色,能将已编码的输入转换成已编码的输出,这里输入和输出的编码是不同的。输入使能信号必须接在解码器上使其正常工作,否则输出将会是一个无效的码字。解码在多路复用、 七段数码管和内存地址解码等应用中是必要的。

二进制解码器通常实现为独立集成电路(IC)或更复杂的IC的一部分。在后一种情况下,可以通过诸如VHDL或Verilog等的硬件描述语言来合成解码器。广泛使用的解码器通常以标准化IC的形式提供。

原理

[编辑]解码器可以由与门或与非门来负责输出。若使用与门,当所有的输入均为高电平时,输出才为高电平,这样的输出称为“高电平有效”的输出;若使用与非门,则当所有的输入均为高电平时,输出才为低电平,这样的输出称为“低电平有效”的输出。

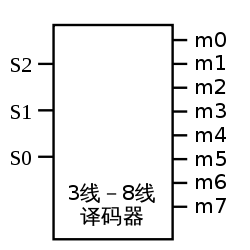

更复杂的解码器是n线-2n线类型的二进制解码器。这类解码器是一种组合逻辑电路,能从已编码的n个输入,将二进制资讯转换为2n个独特的输出中最大个数的输出。我们说2n个输出的最大个数,是因为当n位已编码资讯中有未使用的位组合时,解码器可能会有少于2n个输出。

解码器包括2线-4线解码器、3线-8线解码器或4线-16线解码器。在有使能信号输入的情况下,2个2线-4线解码器可以组成1个3线-8线解码器,同样,2个3线-8线解码器可以组成1个4线-16线解码器。在这类电路设计中,2个3线-8线解码器的使能输入都来自于第四个输入端,这一输入在2个3线-8线解码器间起到了选择器的作用t。这使得第四个输入端可以使2个解码器中的任何一个工作,其中第一个解码器产生输出D(0)至D(7),第二个解码器产生输出D(8)至D(15)。包含使能输入的解码器又称解码器-多路分配器。因此,将第四个输入端作为2个解码器共享的输出就能组成1个4线-16线解码器,能产生16个输出。[1]

二进制解码器通常实现为独立集成电路(IC)或更复杂的IC的一部分。在后一种情况下,可以通过诸如VHDL或Verilog之类的硬件描述语言来合成解码器。广泛使用的解码器通常以标准化IC的形式提供。

二进制到一元解码器

[编辑]二进制到一进制解码器将每个二进制值转换为其关系的一进制表示形式。与n选1(单发)解码器不同,可以为每个输入值声明多个输出位。这些解码器可用于每个位均等加权的DAC,以及需要二进制掩码或窗口的电路。

功能表

[编辑]

- 输入:s0,s1,s2

- 输出:最小项m0,m1,…,m7

行选择

[编辑]

大多数随机存取存储器使用n线-2n线解码器来将地址总线上已选择的地址转换为行地址选择线中的一个。[2]

指令解码器

[编辑]在CPU设计中,指令解码器是CPU的一部分,能将存储在指令寄存器或微程序指令中的位元转换为能控制CPU其他部分的控制信号。

8个寄存器组成的简单CPU会使用指令解码器中的3线-8线逻辑解码器来选择寄存器文件的源寄存器并输出到ALU以及目的寄存器中,以接受ALU的输出。典型的CPU指令解码器也包括其他很多组件。[3]

参见

[编辑]参考资料

[编辑]- ^ Binary to unary decoder for a video digital to analog converter. 1992-08-10 [2021-03-24]. (原始内容存档于2021-04-09).

- ^ Abdelhadi, Ameer M. S. Architecture of block-RAM-based massively parallel memory structures : multi-ported memories and content-addressable memories. University of British Columbia. 2016 [2021-04-28]. (原始内容存档于2021-04-30).

- ^ AmeerAbdelhadi/Indirectly-Indexed-2D-Binary-Content-Addressable-Memory-BCAM. GitHub. [2020-02-29]. (原始内容存档于2020-12-10) (英语).