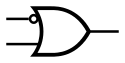

蘊含門

外觀

| 基本邏輯閘 | |

| 緩衝 | 非 |

| 與 | 與非 |

| 或 | 或非 |

| 異或 | 同或 |

| 蘊含 | 蘊含非 |

| 輸入 A B |

輸出 A → B | |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

蘊含門[1](英語:Implies gate,簡稱IMPLY gate)[2]是數碼邏輯電路中的一種邏輯門,主要用來完成布林代數中實質條件、實質蘊涵或蘊涵算子。

另外蘊含門也可以由憶阻器組成,且只需要由兩個憶阻器即可組成[3][4],由於布林代數的特性可使其他布林函數化成由邏輯蘊含表示[5],因此利用蘊含門與憶阻器來設計電晶體可以大幅縮小體積[6]。

性質

[編輯]| 輸入 A B |

輸出 A → B | |

| X | 1 | 1 |

| 0 | 0 | 1 |

| 1 | 0 | 0 |

- 如果B為邏輯真, 無論A為任何值都會輸出邏輯真的訊號。

- 其中,X代表輸入的是無論何值皆可。

- 如果B為邏輯假, 並且A為邏輯假, 才會輸出邏輯真的訊號。

- 其餘情況則輸出邏輯假的訊號。

- 蘊含門可以用來判斷兩輸入的或是否為第二輸入。

概述

[編輯]| 表達式 | 符號 | 功能表 | ||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ANSI/IEEE | IEC | |||||||||||||||||

|

|

| ||||||||||||||||

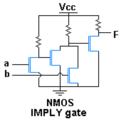

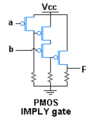

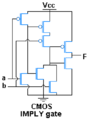

電路實現

[編輯]複合邏輯門

[編輯]

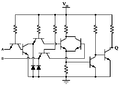

大部分的邏輯門都可以用蘊含門組合而成,例如與非門可以用兩個蘊含門組合而成[9]:

其他邏輯門

[編輯]蘊含非閘

[編輯]蘊含非閘,簡稱NIMPLY gate是數碼邏輯電路中實現非蘊涵的一種邏輯門。

這種運作方式的元件已在生物學的邏輯信號中有相關研究。[10]

| 表達式 | 符號 | 功能表 | ||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ANSI/IEEE | IEC | |||||||||||||||||

|

|

| ||||||||||||||||

參見

[編輯]查看維基詞典中的詞條「implication gate」。

參考文獻

[編輯]- ^ 電腦名詞譯名 (頁面存檔備份,存於互聯網檔案館) Implies gate→蘊含門 iicm.org.tw [2015-9-30]

- ^ 蘊含閘 implication gate. 國家教育研究院. [2019-04-09]. (原始內容存檔於2019-06-03).

- ^ imply gate (頁面存檔備份,存於互聯網檔案館) zigwap.com [2015-9-30]

- ^ 可配置性憶阻器現身 CPU掰掰[永久失效連結] 雙憶阻元件實現蘊含門 eettaiwan.com [2015-9-30]

- ^ Imply Logic Implementation of Carry Save Adder Using Memristors (頁面存檔備份,存於互聯網檔案館) ijera.com [2015-9-30]

- ^ Kanellos, Michael. HP makes memory from a once theoretical circuit. CNET News.com. 2008-04-30 [2008-04-30]. (原始內容存檔於2021-02-20).

- ^ Gregory S.;Stewart Duncan R.;Williams R. Stanley Strukov,Dmitri B.;Snider. The missing memristor found.Nature, 453:80–83, may 2008, [2015-9-30]

- ^ Memristor-Based Material Implication IMPLY Logic: Design Principles and Methodo logies (頁面存檔備份,存於互聯網檔案館) technion.ac.il [2015-10-1]

- ^ Disclosing the secrets of memristors and implication logic (頁面存檔備份,存於互聯網檔案館) web.cecs.pdx.edu [2015-9-30]

- ^ Design and processing performance of synthetic N-IMPLY gates in human cells. (頁面存檔備份,存於互聯網檔案館) From Programmable single-cell mammalian biocomputers Simon Ausländer, David Ausländer, Marius Müller, Markus Wieland & Martin Fussenegger Nature (2012) doi:10.1038/nature11149