PCI Express

PCI Express標誌 | |

| 英文全名 | Peripheral Component Interconnect Express |

|---|---|

| 發明日期 | 2003年 |

| 發明者 | |

| 闊度 | 1-32 |

| 最多連接 | 1 |

| 頻寬 | 單連結(x1)和16通道(x16)連接,雙單工,每個方向:

|

| 類別 | 串行 |

| 熱插拔 | 支援(依格式而定) |

| 外置介面 | 支援,通過 PCI Express OCuLink 和外接線,例如 Thunderbolt |

Peripheral Component Interconnect Express,簡稱PCI-E,官方簡稱PCIe,是電腦匯流排的一個重要分支,它沿用既有的PCI編程概念及訊號標準,並且構建了更加高速的串行通訊系統標準。目前這一標準由PCI-SIG組織制定和維護。PCIe僅應用於內部互連。由於PCIe是基於既有的PCI系統,所以只需修改實體層而無須修改軟體就可將現有PCI系統轉換為PCIe。

PCIe擁有更快的速率,所以幾乎取代了以往所有的內部匯流排(包括AGP和PCI)。現在英特爾和AMD已採用單晶片組技術,取代原有的南橋和北橋方案。

除此之外,PCIe裝置能夠支援熱拔插以及熱交換特性,目前支援的三種電壓分別為+3.3V、3.3Vaux以及+12V。

考慮到現在顯示卡功耗的日益增加,PCIe而後在規範中改善了直接從插槽中取電的功率限制,×16的最大提供功率一度達到了75W[1],相對於AGP 8X介面有了很大的提升。

PCIe保證了相容性,支援PCI的作業系統無需進行任何更改即可支援PCIe總線。這也給使用者的升級帶來方便。由此可見,PCIe最大的意義在於它的通用性,不僅可以讓它用於南橋和其他裝置的連接,也可以延伸到晶片組間的連接,甚至也可以用於連接圖形處理器,這樣,整個I/O系統重新統一起來,將更進一步簡化電腦系統,增加電腦的可移植性和模組化。

歷史

[編輯]在2001年的春季英特爾開發者論壇(IDF)上Intel公布取代PCI匯流排的第三代I/O技術,被稱為「3GIO」。該匯流排的規範由Intel支援的AWG(Arapahoe Work Group)負責制定。2002年4月17日,AWG正式宣布3GIO 1.0規範草稿制定完畢,移交PCI特殊興趣組織(PCI-SIG)進行稽核,2002年7月23日經過稽核後正式公布,改名為「PCI Express」,並根據開發藍圖在2006年正式推出Spec 2.0(2.0規範)。[2][3]2019年5月28日,PCI-SIG官方發布了PCIe 5.0的1.0版基礎規範,規範主要定義了PCIe5.0的架構(architecture)、互聯屬性規範(interconnect attributes)、網路結構管理(fabric management)以及編程介面(programming interface)等內容[4]。

| 版本 | 推出 | Line 編碼 | 每通道 傳輸率[i] |

頻寬(每個方向)[i] | |||||

|---|---|---|---|---|---|---|---|---|---|

| x1 | x2 | x4 | x8 | x16 | |||||

| 1.0 | 2003 | NRZ | 8b/10b | 2.5 GT/s | 0.250 GB/s | 0.500 GB/s | 1.000 GB/s | 2.000 GB/s | 4.000 GB/s |

| 2.0 | 2007 | 5.0 GT/s | 0.500 GB/s | 1.000 GB/s | 2.000 GB/s | 4.000 GB/s | 8.000 GB/s | ||

| 3.0 | 2010 | 128b/130b | 8.0 GT/s | 0.985 GB/s | 1.969 GB/s | 3.938 GB/s | 7.877 GB/s | 15.754 GB/s | |

| 4.0 | 2017 | 16.0 GT/s | 1.969 GB/s | 3.938 GB/s | 7.877 GB/s | 15.754 GB/s | 31.508 GB/s | ||

| 5.0[5][6] | 2019[7][8] | 32.0 GT/s[ii] | 3.938 GB/s | 7.877 GB/s | 15.754 GB/s | 31.508 GB/s | 63.015 GB/s | ||

| 6.0 | 2021 | PAM-4 FEC |

1b/1b 242B/256B FLIT |

64.0 GT/s 32.0 GBd |

7.563 GB/s | 15.125 GB/s | 30.250 GB/s | 60.500 GB/s | 121.000 GB/s |

| 7.0 | 2025 (預計) |

128.0 GT/s 64.0 GBd |

15.125 GB/s | 30.250 GB/s | 60.500 GB/s | 121.000 GB/s | 242.000 GB/s | ||

以PCIe 2.0為例,每秒5GT(Gigatransfer)原始數據傳輸率,編碼方式為8b/10b(每10個位元只有8個有效數據),即有效頻寬為4Gb/s = 500MByte/s。

PCI Express與其他傳輸規格比較

[編輯]

PCIe的規範主要是為了提升電腦內部所有匯流排的速度,因此頻寬有多種不同規格標準,其中PCIe ×16是特別為顯示卡所設計。AGP的資料傳輸效率最高為2.1GB/s,不過對上PCIe ×16的8GB/s,很明顯的就分出勝負,但8GB/s是指資料傳輸的理想值,並不是使用PCIe介面的顯示卡,就能夠有突飛猛進的效能表現,實際的測試數據並不會有這麼大的差異存在。 [9][10]

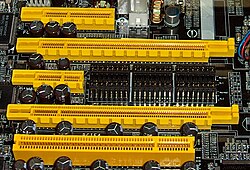

| 傳輸通道數 | 腳Pin總數 | 主介面區Pin數 | 總長 度 | 主介面區長度 |

|---|---|---|---|---|

| x1 | 36 | 14 | 25 mm | 7.65 mm |

| x4 | 64 | 42 | 39 mm | 21.65 mm |

| x8 | 98 | 76 | 56 mm | 38.65 mm |

| x16 | 164 | 142 | 89 mm | 71.65 mm |

| 規格 | 匯流排寬度 | 工作時脈 | 資料速率 |

|---|---|---|---|

| PCI 2.3 | 32位元 | 33/66 MHz | 133/266 MB/s |

| PCI-X 1.0 | 64位元 | 66/100/133 MHz | 533/800/1066 MB/s |

| PCI-X 2.0(DDR) | 64位元 | 133 MHz | 2.1 GB/s |

| PCI-X 2.0(QDR) | 64位元 | 133 MHz | 4.2 GB/s |

| AGP 2X | 32位元 | 66 MHz | *2=532 MB/s |

| AGP 4X | 32位元 | 66 MHz | *4=1.0 GB/s |

| AGP 8X | 32位元 | 66 MHz | *8=2.1 GB/s |

| PCI-E 1.0 X1 | 1位元 | 2.5 GHz | 250 MB/s |

| PCI-E 1.0 X2 | 2位元 | 2.5 GHz | 500 MB/s |

| PCI-E 1.0 X4 | 4位元 | 2.5 GHz | 1 GB/s |

| PCI-E 1.0 X8 | 8位元 | 2.5 GHz | 2 GB/s |

| PCI-E 1.0 X16 | 16位元 | 2.5 GHz | 4 GB/s |

計算公式:PCI-E串行匯流排頻寬(MB/s) = 串行匯流排時脈頻率(MHz)* 串行匯流排位寬(bit/8 = B)* 串行匯流排管線* 編碼方式* 每時鐘傳輸幾組資料(cycle),例:雙工PCI-E 1.0 X1,其頻寬 = 2500*1/8*1*8/10*1*2=500 MB/s。

PCI Express 1.0匯流排頻率2500 MHz,這是在100 MHz的基準頻率通過鎖相環振盪器(Phase Lock Loop,PLL)達到的。PCI-E 2.0匯流排頻率從2.5GHz提高到5GHz,3.0則提高到8GHz,編碼方式變成128/130。

PCI Express的硬體協定

[編輯]PCIe的連接是建立在一個單向的序列的(1-bit)對等連接基礎之上,這稱之為通道(lane)。這一點上PCIe連接與早期PCI連接形成鮮明對比,PCI連接基於匯流排控制,所有裝置共享雙向32位元並列匯流排。PCIe是一個多層協定,由事務層,資料交換層和實體層構成。實體層又可進一步分為邏輯子層和電氣子層。邏輯子層又可分為物理代碼子層(PCS)和媒介接入控制子層(MAC)。這些術語借用自 IEEE 802 網路協定模型。PCIe通過ASPM協定進行電源管理。

實體層

[編輯]

於使用電力方面,每組管線使用兩個單向的低電壓差分訊號(LVDS)合計達到2.5 Gbit/s。傳送及接收不同資料會使用不同的傳輸通道,每一通道可運作四項資料。兩個PCIe裝置之間的連接成為「連結」,這形成1組或更多的傳輸通道。各個裝置最少支援1傳輸通道(x1)的連結。也可以有2,4,8,16,32個通道的連結。這可以更好的提供雙向相容性(x2模式將用於內部介面而非插槽模式)。PCIe卡能使用在至少與之傳輸通道相當的插槽上(例如x1介面的卡也能工作在x4或x16的插槽上)。一個支援較多傳輸通道的插槽可以建立較少的傳輸通道(例如8個通道的插槽能支援1個通道)。PCIe裝置之間的連結將使用兩裝置中較少通道數的作為標準。一個支援較多通道的裝置不能在支援較少通道的插槽上正常工作,例如x4介面的卡不能在x1的插槽上正常工作(插不入),但它能在x4的插槽上只建立1個傳輸通道(x1)。PCIe卡能在同一資料傳輸通道內傳輸包括中斷在內的全部控制資訊。這也方便與PCI的相容。多傳輸通道上的資料傳輸採取交叉存取,這意味著連續位元組交叉存取在不同的通道上。這一特性被稱之為「資料條紋」,需要非常複雜的硬體支援連續資料的同步存取,也對連結的資料吞吐量要求極高。由於資料填充的需求,資料交叉存取不需要縮小封包。與其它高速數傳輸協定一樣,時鐘資訊必須嵌入訊號中。在實體層上,PCIe採用常見的8B/10B代碼方式來確保連續的1和0字串長度符合標準,這樣保證接收端不會誤讀。編碼方案用10位編碼位元代替8個未編碼位元來傳輸資料,占用20%的總頻寬。到了PCIe 3.0,採用128B/130B代碼方式,僅占用1.538%的總頻寬。有些協定(如SONET)使用另外的編碼結構如「不規則」在資料流中嵌入時鐘資訊。PCIe的特性也定義一種「不規則化」的運算方法,但這種方法與SONET完全不同,它的方法主要用來避免資料傳輸過程中的資料重複而出現資料散射。第一代PCIe採用2.5GT/s單訊號傳輸率,PCI-SIG計劃在未來版本中增強到5~10GT/s。

資料鏈路層

[編輯]資料鏈路層採用按序的交換層資訊包(Transaction Layer Packets,TLPs),是由交換層生成,按32位元迴圈冗餘校驗碼(CRC,本文中用LCRC)進行資料保護,採用著名的協定(Ack and Nak signaling)的資訊包。TLPs能通過LCRC校驗和連續性校驗的稱為Ack(命令正確應答);沒有通過校驗的稱為Nak(沒有應答)。沒有應答的TLPs或者等待逾時的TLPs會被重新傳輸。這些內容儲存在資料鏈路層的快取內。這樣可以確保TLPs的傳輸不受電子噪音干擾。PCIe對於ACK有所規範,在收到TLP封包之後,在一定時間內必須回應ACK,也就是ACK延遲(ACK Latency)的等待時間。因應ACK/NAK流程的需要,必須實作出重新播送緩衝器(Replay Buffer)。

TLPs加上Sequence number以及16 位元 CRC 後,被包裹成為資料鏈路層資訊包(Data Link Layer Packet,DLLP),除了資料傳遞外,交握訊號ACK和NAK訊號亦被包裹在資訊包中傳送,除此之外也用來傳送兩個互連裝置的交換層之間的流控制資訊和實現電源管理功能。

事務層

[編輯]PCI Express採用分離交換(資料提交和應答在時間上分離),可保證傳輸通道在目標端裝置等待傳送回應資訊傳送其它資料資訊。

PCI Express採用可信性流控制。這一模式下,一個裝置廣播它可接收快取的初始可信號誌。連結另一方的裝置會在傳送資料時統計每一傳送的TLP所占用的可信號誌,直至達到接收端初始可信訊號最高值。接收端在處理完畢快取中的TLP後,它會回送傳送端一個比初始值更大的可信號誌。可信訊號統計是客製化的標準計數器,相比於其他方法,如基於握手的傳輸協定,這一模式的優勢在於可信訊號的回傳反應時間不會影響系統效能,因為如果雙方裝置的快取足夠大,是不會出現達到可信訊號最高值的情況,這樣傳送資料不會停頓。

第一代PCIe標稱可支援每傳輸通道單向每秒250 MB的資料傳輸率。這一數字是根據物理訊號率2500 Mbit/s除以編位元速率(10位/每位元組)計算而得。這意味著一個16通道(x16)的PCIe卡理論上可以達到單向250*16=4000 MB/s(3.7 GB/s)。實際的傳輸率要根據資料有效載荷率,即依賴於資料的本身特性,這是由更高層(軟體)應用程式和中間協定層決定。

PCI Express與其它高速序列連接系統相似,它依賴於傳輸的強健性(CRC校驗和ACK)。長時間連續的單向資料傳輸(如高速儲存裝置)可以達到>95%的PCIe通道資料傳輸利用率。這樣的傳輸受益於增加的傳輸通道(x2, x4 等)。但大多數應用程式如USB或乙太網路控制器會把傳輸內容拆成小的封包,同時還會強制加上確認訊號。這類資料傳輸由於增加封包的解析和強制中斷,降低傳輸通道的效率。作為一個在同一個印刷電路板(PCB)裝置間的通訊協定,它不需要達到其他遠距離通訊協定要求的高資料傳輸錯誤容忍度,而且,這種效率的降低並非只出現在PCIe上。

引腳

[編輯]下表列出在邊緣連接器上的PCI Express卡兩側的導線。在印刷電路板(PCB)的焊接側為A側,並且組件側的B側。[11]PRSNT1# 和PRSNT2# 引腳必須比其餘稍短,以確保熱插入卡完全插入。該WAKE# 引腳採用全電壓喚醒計算機,但必須拉高從備用電源,以表明該卡是能夠喚醒。[12]

| 引腳 | B側 | A側 | 描述 | 引腳 | B側 | A側 | 描述 | |

|---|---|---|---|---|---|---|---|---|

| 1 | +12 V | PRSNT1# | 必須連接到最遠PRSNT2# 引腳 | 50 | HSOp (8) | Reserved | 通道8傳輸數據,+和− | |

| 2 | +12 V | +12 V | 51 | HSOn (8) | Ground | |||

| 3 | +12 V | +12 V | 52 | Ground | HSIp (8) | 通道8接收數據,+和− | ||

| 4 | Ground | Ground | 53 | Ground | HSIn (8) | |||

| 5 | SMCLK | TCK | SMBus和JTAG埠引腳 | 54 | HSOp (9) | Ground | 通道9傳輸數據,+和− | |

| 6 | SMDAT | TDI | 55 | HSOn (9) | Ground | |||

| 7 | Ground | TDO | 56 | Ground | HSIp (9) | 通道9接收數據,+和− | ||

| 8 | +3.3 V | TMS | 57 | Ground | HSIn (9) | |||

| 9 | TRST# | +3.3 V | 58 | HSOp (10) | Ground | 通道10傳輸數據,+和− | ||

| 10 | +3.3 V aux | +3.3 V | 備用電源 | 59 | HSOn (10) | Ground | ||

| 11 | WAKE# | PERST# | 鏈結啟用;基本復位 | 60 | Ground | HSIp (10) | 通道10接收數據,+和− | |

| Key notch | 61 | Ground | HSIn (10) | |||||

| 12 | CLKREQ# | Ground | 要求運行的時鐘 | 62 | HSOp (11) | Ground | 通道11傳輸數據,+和− | |

| 13 | Ground | REFCLK+ | 參考時鐘差分對 | 63 | HSOn (11) | Ground | ||

| 14 | HSOp (0) | REFCLK− | 64 | Ground | HSIp (11) | 通道11接收數據,+和− | ||

| 15 | HSOn (0) | Ground | 65 | Ground | HSIn (11) | |||

| 16 | Ground | HSIp (0) | 通道0接收數據,+和− | 66 | HSOp (12) | Ground | 通道12傳輸數據,+和− | |

| 17 | PRSNT2# | HSIn (0) | 67 | HSOn (12) | Ground | |||

| 18 | Ground | Ground | 68 | Ground | HSIp (12) | 通道12接收數據,+和− | ||

| PCI Express ×1卡於引腳18結束 | 69 | Ground | HSIn (12) | |||||

| 19 | HSOp (1) | Reserved | 通道1傳輸數據,+和− | 70 | HSOp (13) | Ground | 通道13傳輸數據,+和− | |

| 20 | HSOn (1) | Ground | 71 | HSOn (13) | Ground | |||

| 21 | Ground | HSIp (1) | 通道1接收數據,+和− | 72 | Ground | HSIp (13) | 通道13接收數據,+和− | |

| 22 | Ground | HSIn (1) | 73 | Ground | HSIn (13) | |||

| 23 | HSOp (2) | Ground | 通道2傳輸數據,+和− | 74 | HSOp (14) | Ground | 通道14傳輸數據,+和− | |

| 24 | HSOn (2) | Ground | 75 | HSOn (14) | Ground | |||

| 25 | Ground | HSIp (2) | 通道2接收數據,+和− | 76 | Ground | HSIp (14) | 通道14接收數據,+和− | |

| 26 | Ground | HSIn (2) | 77 | Ground | HSIn (14) | |||

| 27 | HSOp (3) | Ground | 通道3傳輸數據,+和− | 78 | HSOp (15) | Ground | 通道15傳輸數據,+和− | |

| 28 | HSOn (3) | Ground | 79 | HSOn (15) | Ground | |||

| 29 | Ground | HSIp (3) | 通道3接收數據,+和− | 80 | Ground | HSIp (15) | 通道15接收數據,+和− | |

| 30 | Reserved | HSIn (3) | 81 | PRSNT2# | HSIn (15) | |||

| 31 | PRSNT2# | Ground | 82 | Reserved | Ground | |||

| 32 | Ground | Reserved | ||||||

| PCI Express ×4卡於引腳32結束 | ||||||||

| 33 | HSOp (4) | Reserved | 通道4傳輸數據,+和− | |||||

| 34 | HSOn (4) | Ground | ||||||

| 35 | Ground | HSIp (4) | 通道4接收數據,+和− | |||||

| 36 | Ground | HSIn (4) | ||||||

| 37 | HSOp (5) | Ground | 通道5傳輸數據,+和− | |||||

| 38 | HSOn (5) | Ground | ||||||

| 39 | Ground | HSIp (5) | 通道5接收數據,+和− | |||||

| 40 | Ground | HSIn (5) | ||||||

| 41 | HSOp (6) | Ground | 通道6傳輸數據,+和− | |||||

| 42 | HSOn (6) | Ground | ||||||

| 43 | Ground | HSIp (6) | 通道6接收數據,+和− | 圖例 | ||||

| 44 | Ground | HSIn (6) | 接地引腳 | 零電壓基準 | ||||

| 45 | HSOp (7) | Ground | 通道7傳輸數據,+和− | 電源引腳 | 為PCIe卡供電 | |||

| 46 | HSOn (7) | Ground | 輸出引腳 | 從PCIe卡到主機板的訊號 | ||||

| 47 | Ground | HSIp (7) | 通道7接收數據,+和− | 輸入引腳 | 從主機板到PCIe卡的訊號 | |||

| 48 | PRSNT2# | HSIn (7) | 漏極開路 | 可拉至低電平或感應到多個卡 | ||||

| 49 | Ground | Ground | 檢測引腳 | 卡連接在一起 | ||||

| PCI Express ×8卡於引腳49結束 | 備用 | 目前沒有使用,不連接 | ||||||

格式標準

[編輯]

- 半高卡

- Mini PCIe:用以代替Mini PCI卡(支援x1 PCIe、USB 2.0和SMBus匯流排介面)。

- ExpressCard:類似PC卡介面標準(支援x1 PCIe、USB 2.0/3.0、熱插拔)。

- PCI Express ExpressModule:支援熱插拔的介面標準,用於伺服器和工作站上。

- XMC:類似CMC/PMC介面標準(支援x4 PCIe或串行RapidI/O)。

- AdvancedTCA:用以代替Compact PCI卡,支援串行背板拓撲結構基礎。

- AMC:AdvancedTCA規範的補充,支援處理器和I/O模組在ATCA板上(x1、x2、x4或x8 PCIe)。

- PCI Express外置接線[13]。

- Mobile PCI Express Module(MXM)輝達所發明的圖形模組規範。

- Advanced eXpress I/O Module(AXIOM)圖形模組,由ATI認可。

- Thunderbolt

- M.2

- U.2

競爭協定

[編輯]基於高速序列構架產生了很多傳輸標準,包括HyperTransport、InfiniBand、RapidIO和StarFabric等等。這些標準均有業界的不同企業支援,背後也都有大量的資金投入標準的研究開發,所以每一標準都聲稱自己與眾不同,獨占優勢。主要的差異在於可延伸性、靈活性與反應時間、單位成本的取捨平衡各不相同。其中的一個例子是在傳輸包上增加一個複雜的頭資訊以支援複雜路由傳輸(PCI Express不支援這種方式)。這樣的資訊增加降低了介面的有效頻寬也使傳輸更複雜,但是相應創造了新的軟體支援此功能。這種架構下需要軟體追蹤網路拓撲結構的變化以實現系統支援熱插拔。InfiniBand和StarFabric標準即能實現這一功能。另一個例子是縮小資訊包以減少反應時間。較小的資訊包意味著包頭占用了包的更大百分比,這樣又降低了有效頻寬。能實現此功能的標準是RapidIO和HyperTransport。PCI Express取中庸之道,定位於設計成一種系統互連介面而非一種裝置介面或路由網路協定。另外為了針對軟體透明,它的設計目標限制了它作為協定,也在某種程度上增加了它的反應時間。

應用與前景

[編輯]

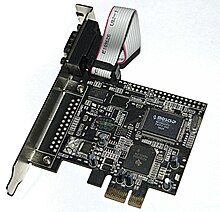

在2005年,PCIe已近乎成為新的個人電腦主機板標準。關於此有不少評論,但最基本的原因是它對於軟體開發者完全透明——為PCI所設計的作業系統可以不做任何代碼修改來啟動PCIe裝置。其二,它能增強系統效能,還有強有力的品牌認知。各類網卡、音效卡、顯示卡,以及當下的NVMe固態硬碟都使用了PCIe標準。下面為主流的使用PCIe 的外設產品。

顯示卡

[編輯]大部分新型的AMD或NVIDIA顯示卡都使用PCIe標準。NVIDIA在它新開發的SLI上採用PCIe的高速資料傳輸,這使得兩塊相同晶片組顯示卡可同時工作於一台電腦之上。AMD公司也基於PCIe開發一種兩個GPU一同運作的技術,稱為CrossFire。

硬碟

[編輯]當下主流的固態硬碟介面有M.2、U.2、PCIe、SATA、SATA Express、SAS等。M.2和U.2可選PCIe介面[14]。NVMe協定是目前最高效的PCIe SSD協定標準。

參考文獻

[編輯]- ^ Desktop Boards—Some PCI Express* Graphics cards require extra power. 2004-06-03 [2010-11-12]. (原始內容存檔於2010-07-22).

25W-75W graphics cards are powered through the desktop board's PCI Express x16 connector

- ^ 2.0 2.1 PCI Express 4.0 Frequently Asked Questions. pcisig.com. PCI-SIG. [2014-05-18]. (原始內容存檔於2014-05-18).

- ^ 3.0 3.1 PCI Express 3.0 Frequently Asked Questions. pcisig.com. PCI-SIG. [2014-05-01]. (原始內容存檔於2014-02-01).

- ^ PCI-SIG官网通信接口规范. (原始內容存檔於2019-07-02).

- ^ PCIe 4.0 Heads to Fab, 5.0 to Lab. EE Times. 2016-06-26 [2016-08-27]. (原始內容存檔於2016-08-28).

- ^ Archived copy. [2016-08-18]. (原始內容存檔於2016-08-19).

- ^ https://www.tomshardware.com/news/pci-sig-releases-final-pcie-5-spec,39521.html

- ^ Doubling Bandwidth in Under Two Years: PCI Express® Base Specification Revision 5.0, Version 0.9 is Now Available to Members. pcisig.com. [2018-12-12]. (原始內容存檔於2018-12-23) (英語).

- ^ Mechanical Drawing for PCI Express Connector. [2007-12-07]. (原始內容存檔於2007-12-08).

- ^ FCi schematic for PCIe connectors (PDF). [2007-12-07].[永久失效連結]

- ^ What is the A side, B side configuration of PCI cards. Frequently Asked Questions. Adex Electronics. 1998 [Oct 24, 2011]. (原始內容存檔於2011-11-02).

- ^ PCI Express Card Electromechanical Specification Revision 2.0

- ^ PCI Express External Cabling 1.0 Specification. [2007-02-09]. (原始內容存檔於2007-02-10).

- ^ 存档副本. [2019-07-22]. (原始內容存檔於2019-07-22).

參見

[編輯]

| ||||||||||||||||||||||||||||||||||||||||||